Лабораторная работа №13

Проектирование, описание на языке VHDL и моделирование схем последовательной логики.

Выполнил:

студент группы ЭC-31

Матылицкий И. В.

Цель работы: Изучить методы и приёмы проектирования и моделирования схем последовательной логики – триггеров, регистров, счётчиков - на языке VHDL.

Выполнение работы

Задание:

1. Разработать на языке VHDL поведенческую модель описания D-триггера. Запись информации со входа D-триггера на его выход Qдолжна происходить по положительному фронту.

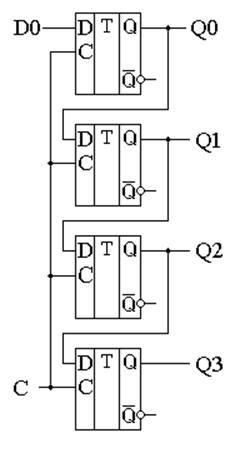

2. Разработать модель последовательного регистра. Последовательный регистр (регистр сдвига) обычно служит для преобразования последовательного кода в параллельный и наоборот. Схема регистра, осуществляющего преобразование последовательного кода в параллельный, приведена на рисунке.

1. Разработано VHDLописание заданного D-триггера:

library IEEE;

use IEEE.std_logic_1164.all;

entity D_DynPosC_FF is

port(D,C:in std_logic;

Q,nQ:out std_logic:='0');

end;

architecture D_DynPosC_FF of D_DynPosC_FF is

begin

process(C)

begin

if ((C'Last_value='0') and (C='1')) then

Q<=D;

nQ<=not D;

end if;

end process;

end;

library IEEE;

use IEEE.std_logic_1164.all;

package Triggers is

component D_DynPosC_FF

port(D,C:in std_logic;

Q,nQ:out std_logic:='0');

end component;

end package;

package body Triggers is

end package body;

2. Разработано иерархическое VHDL-описание заданного регистра:

library IEEE;

use IEEE.std_logic_1164.all;

use work.Triggers.all;

entity sreg is

port(D0,C:in std_logic;

Q:out std_logic_vector(0 to 3):="0000";

nQ:out std_logic_vector(0 to 3):="0000");

end;

architecture sreg of sreg is

signal nets:std_logic_vector(0 to 4);

begin

sregp:for i in 0 to 3 generate

regl:D_DynPosC_FF

port map(C=>C,D=>nets(i),Q=>nets(i+1),nQ=>nQ(i));

end generate;

nets(0)<=D0;

nets_bind:for i in 1 to 4 generate

Q(i-1)<=nets(i);

end generate;

end;

3. Разработана графическая модель заданного регистра:

---------------------------------------------------------------------------------------------------

--

-- Title : No Title

-- Design : nLab_13_design

-- Author : Buffovich

-- Company : Adequatus

--

---------------------------------------------------------------------------------------------------

--

-- File : F:\Workplace Buffovich\Math Models\nLab_13\nLab_13_do\nLab_13_design\compile\S_reg.vhd

-- Generated : Tue May 22 04:22:01 2007

-- From : F:/Workplace Buffovich/Math Models/nLab_13/nLab_13_do/nLab_13_design/src/S_reg.bde

-- By : Bde2Vhdl ver. 2.6

--

---------------------------------------------------------------------------------------------------

--

-- Description :

--

---------------------------------------------------------------------------------------------------

-- Design unit header --

library IEEE;

use IEEE.std_logic_1164.all;

use work.Triggers.all;

entity S_reg is

port(

C : in STD_LOGIC;

D0 : in STD_LOGIC;

Q0 : out STD_LOGIC;

Q1 : out STD_LOGIC;

Q2 : out STD_LOGIC;

Q3 : out STD_LOGIC;

nQ0 : out STD_LOGIC;

nQ1 : out STD_LOGIC;

nQ2 : out STD_LOGIC;

nQ3 : out STD_LOGIC

);

end S_reg;

architecture S_reg of S_reg is

---- Signal declarations used on the diagram ----

signal NET191 : STD_LOGIC;

signal NET203 : STD_LOGIC;

signal NET211 : STD_LOGIC;

signal NET219 : STD_LOGIC;

signal NET61 : STD_LOGIC;

signal NET73 : STD_LOGIC;

signal NET792 : STD_LOGIC;

signal NET852 : STD_LOGIC;

begin

---- Component instantiations ----

U1 : D_DynPosC_FF

port map(

C => C,

D => D0,

Q => NET792,

nQ => NET203

);

nQ2 <= NET219;

nQ1 <= NET211;

nQ3 <= NET852;

U2 : D_DynPosC_FF

port map(

C => C,

D => NET792,

Q => NET61,

nQ => NET211

);

U3 : D_DynPosC_FF

port map(

C => C,

D => NET61,

Q => NET73,

nQ => NET219

);

U4 : D_DynPosC_FF

port map(

C => C,

D => NET73,

Q => NET191,

nQ => NET852

);

Q0 <= NET792;

Q2 <= NET73;

Q1 <= NET61;

Q3 <= NET191;

nQ0 <= NET203;

end S_reg;

4. Разработана имитационная модель заданного регистра:

library IEEE;

use IEEE.std_logic_1164.all;

entity s_reg_unit is

generic(N:natural:=4);

port(D0,C:in std_logic;

Q:out std_logic_vector(0 to N-1));

end;

architecture s_reg_unit of s_reg_unit is

begin

process(C)

variable istate:std_logic_vector(0 to N-1);

begin

if ((C'Last_value='0') and (C='1')) then

istate(1 to N-1):=istate(0 to N-2);

istate(0):=D0;

Q<=istate;

end if;

end process;

end;

Вывод:Были изучены и закреплены на практике методы и приёмы проектирования и моделирования схем последовательной логики, способы и средства имитационного моделирования на языке VHDL.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.