Аврамов Р.А. гр. ЭМ-51

Лабораторная работа №6

Проектирование таймера-счетчика

Цель работы: ознакомиться с возможностями, предоставляемыми обобщенным таймером-счетчиком. Получить практические навыки в реализации и тестировании таймера-счетчика на языке VHDL в среде ActiveHDL.

Индивидуальное задание:

|

Вариант |

Тип счета |

Тип счетчика |

Разрядность |

Разрядность предделителя |

|

1 |

Инкремент |

Двоичный |

4 двоичных |

4 |

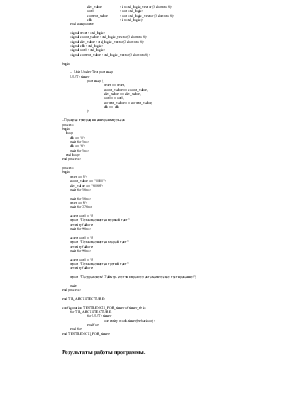

Исходный VHDL-текст реализованного таймера.

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity timer is

port(

reset : in std_logic; -- сброс

count_value : in std_logic_vector (3 downto 0); -- значение для инициализации таймера

div_value : in std_logic_vector (3 downto 0); -- значение делителя счета

out1 : out std_logic; -- выхор таймера

current_value : out std_logic_vector (3 downto 0); -- текущее значение

clk : in std_logic ); -- синхроимпульсы

end timer;

architecture behaviour of timer is

begin

process(

reset,

clk )

variable temp : integer:=0;

variable a : integer:=0;

variable cur_value : std_logic_vector (3 downto 0);

begin

--cur_value (3 downto 0) := count_value (3 downto 0);

if falling_edge(reset)

then

out1<='0';

cur_value (3 downto 0) := "0000";

else if (rising_edge(clk) and reset='0') then

temp := temp + 1;

if (temp = conv_integer(unsigned(div_value))) then

out1<='0';

temp:=0;

current_value <= cur_value;

cur_value(3 downto 0) := cur_value(3 downto 0) + "0001";

if (cur_value (3 downto 0) = count_value (3 downto 0)) then

cur_value (3 downto 0) := "0000";

out1 <= '1';

end if;

end if;

end if;

end if;

end process;

end behaviour;

TestBench

library ieee;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_1164.all;

entity timer_tb is

end timer_tb;

architecture TB_ARCHITECTURE of timer_tb is

component timer

port(

reset : in std_logic;

count_value : in std_logic_vector(3 downto 0);

div_value : in std_logic_vector(3 downto 0);

out1 : out std_logic;

current_value : out std_logic_vector(3 downto 0);

clk : in std_logic );

end component;

signal reset : std_logic;

signal count_value : std_logic_vector(3 downto 0);

signal div_value : std_logic_vector(2 downto 0);

signal clk : std_logic;

signal out1 : std_logic;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.