Однако для сложных схем такая замена может быть совершенно не очевидной.

2.2 Формы описания сигналов

Битовое представление сигналов может быть громоздким. На начальных этапах проектирования могут быть использованы другие |типы данных.

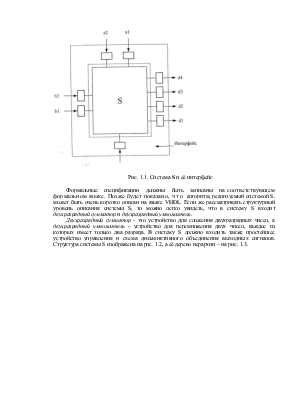

Рис. 2.2. Сигнал С может быть описан как bit_vector и как перечислимый тип

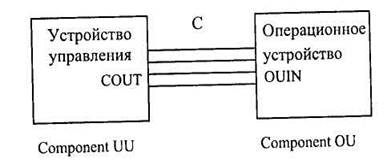

Пусть устройство управления (UU) посылает четырехбитовый код в операционное устройство (OU). Четырехбитовый код определяет операцию, подлежащую выполнению. На рис. 2.2 выходной порт устройства управления имеет имя COUT, входной порт операционного устройства - имя OUIN.

Можно описать сигнал С на битовом уровне

signal С: BIT_VECTOR(0 to 3);

или же как перечислимый тип

type CONTROL is (AND, OR, XOR, ADD, SUB,..., TCOMP);

signal C: CONTROL;

Таким образом, если использовать перечислимый тип, i управляющую информацию можно представлять в мнемоническом виде, т.е. именовать команды UU. При этом в архитектурном теле устройства управления можно было бы использовать операторы назначения сигнала, такие как

COUT <= ADD;

а в архитектурном теле операционного устройства

if (OUIN = ADD) then ...

При таком подходе разработчик модели освобождается от необходимости беспокоиться о низкоуровневых деталях.

Другой вариант описания сигнала С выглядит следующим образом:

subtype CONTROL is INTEGER range 0 to 15;

signal C: CONTROL;

Подтип CONTROL ограничивает диапазон значений, которые могут быть присвоены сигналу С, тем самым обеспечивается некоторый контроль ошибок.

В некоторых случаях может понадобиться как битовый уровень, так и более высокий уровень - типа INTEGER. Для преобразования типов нужны функции. Ниже описаны две функции.

Функция BIN4_TO_INT преобразует битовые векторы в целые числа путем суммирования соответствующих степеней двойки. Функция INT_TO_BIN4 выполняет обратную операцию.

Функция INT_TO_BIN4 приведена ниже в пакете vv_vls. Рекомендуется самостоятельно написать VHDL-код функции BIN4_TO_INT, для образца можно воспользоваться VHDL-кодом функции BIN2_TO_INT, находящемся в теле пакета vv_vls.

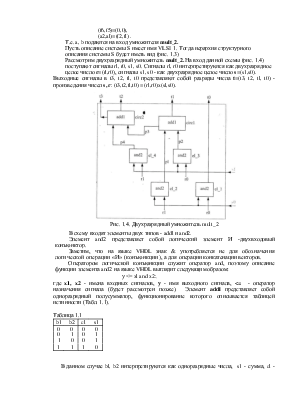

С использованием функций B1N2_TO_INT, INT_TO_B1N4 легко описывается (на алгоритмическом уровне) поведение схем mult_2, adder_2, входящих в схему VLSI_1 (см. гл. 1). Определим функции BIN2_TO_INT, INT_TO_BIN4 в пакете vv_vls.

package vv_vls is

function bin2_to_int (signal w2,w1: bit)

return integer;

function int_to_bin4

(signal INPUT : integer)

return bit_vector;

end vv_vls;

package body vv_vls is

function bin2_to_int -- функция преобразования битового

(signal w2,w1: bit) -- вектора в число

return integer is

variable sum : integer :=0;

begin

if w1 ='1' then

sum :=1;

else

sum :=0;

end if;

if w2 ='1' then

sum := sum+2;

else

sum := sum;

end if;

return sum;

end bin2_to_int;

function int_to_bin4 -- функция преобразования числа

(signal INPUT : integer) -- в битовый вектор

return bit_vector is

variable fout: bit_vector(0 to 3);

variable temp_a: integer:=0;

variable temp_b: integer:=0;

begin

temp_a:=INPUT;

for i in 3 downto 0 loop

temp_b:=temp_a/(2**i);

temp_a:=temp_a rem (2**i);

if (temp_b=1) then

fout(i):='1';

else

fout(i):='0';

end if;

end loop;

return fout;

end int_to_bin4;

end vv_vls;

library work;

use work.vv_vls.all;

entity mult_2 is -- функциональное описание умножителя

port (s1,s0,r1,r0 : in BIT;

t3,t2,t1,t0 : out BIT);

end mult_2;

architecture functional of mult_2 is

use std.vv_vls.all;

signal ss, rr : integer range 0 to 3;

signal tt : integer range 0 to 9;

signal tt_sig : bit_vector (0 to 3);

begin

ss <= bin2_to_int(s1,s0);

rr <= bin2_to_int(r1,r0);

tt <= ss*rr; -- функция умножителя

tt_sig <= int_to_bin4(tt);

t0 <= tt_sig(0); -- формирование выходных сигналов

t1 <= tt_sig(1);

t2 <= tt_sig(2);

t3 <= tt_sig(3);

end functional;

library work;

use work.vv_vls.all;

entity adder_2 is -- функциональное описание -- сумматора

port (a1,b1,a2,b2 : in BIT;

c2,s2,s1 : out BIT);

end adder_2;

architecture functional of adder_2 is

use std.vv_vls.all;

signal aa, bb : integer range 0 to 3;

signal cc : integer range 0 to 7;

signal cc_sig : bit_vector (0 to 3);

begin

aa <= bin2_to_int (a1,b1);

bb <= bin2_to_int (a2,b2);

cc <= aa+bb; -- функция сумматора

cc_sig <= int_to_bin4(cc);

s1 <= cc_sig(0); -- формирование выходных сигналов

s2 <= cc_sig(1);

c2 <= cc_sig(2);

end functional;

Рекомендуем провести моделирование схемы VLSI_1 (разд. 1.1), используя архитектурные тела functional (алгоритмические описания) для объектов проекта mult_2, adder_2 вместо архитектурных тел structure, представленных ранее в разд. 1.1. Чтобы заменить в VHDL-коде архитектурного тела functional схемы VLSI_1 алгоритмическое описание структурным, необходимо сначала перейти к битовому уровню представления входных сигналов а,b (использовать функцию преобразования типа INTEGER в тип BIT_VECTOR), а затем от битового представления выходных сигналов D перейти к типу INTEGER.

2.3 Пример описания автоматов

Схема с обратной связью

Рассмотрим схему, изображенную на рис. 2.3. В нее входит элемент памяти (D-триггер) и комбинационный элемент И. Данная схема описывается в виде двух процессов, причем для описания функционирования D-триггера вводится функция rising_edge.

architecture circ_feedback of some_entity is

signal b: bit;

function rising_edge (signal s : bit ) return boolean

is

begin

return s = '1' and s'event;

end;

begin

process (clk, reset)

begin

if reset = '1' then

c <= '0';

elsif rising_edge(clk)

c <= b;

end if;

end process;

process (a, c) -- комбинационный процесс

begin b <= a and c;

end process;

end circ_feedback ;

3 Рекомендуемая литература

Литература для самостоятельного изучения языка сгруппирована в директории «Справочники VHDL». Каждое из пособий в некоторой степени дополняет остальные, поэтому предпочтение следует отдавать исходя из собственных навыков работы с литературой и текущих потребностей при подготовке к лабораторным работам. Вместе с тем в первую очередь следует обратить внимание на такие материалы

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.