Рисунки к примерам лекции №3

1 Определение напряжений логических состояний цифровых схем

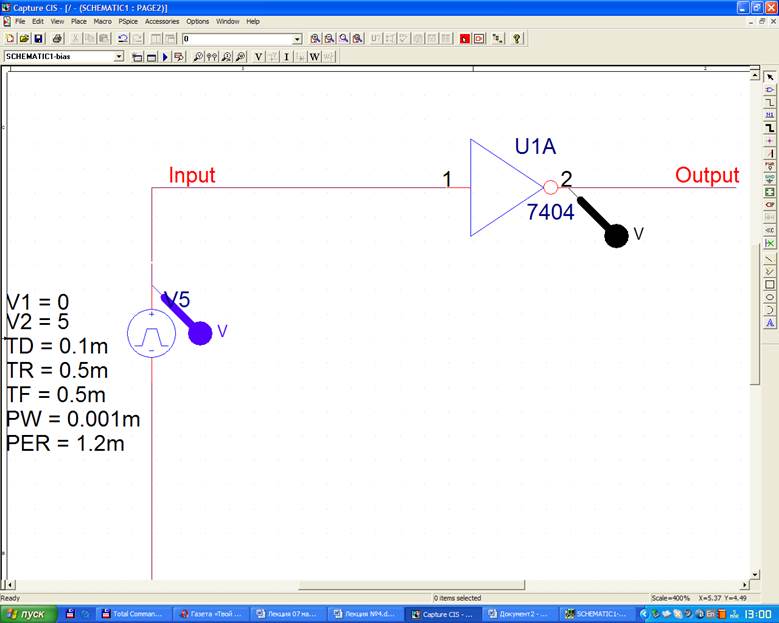

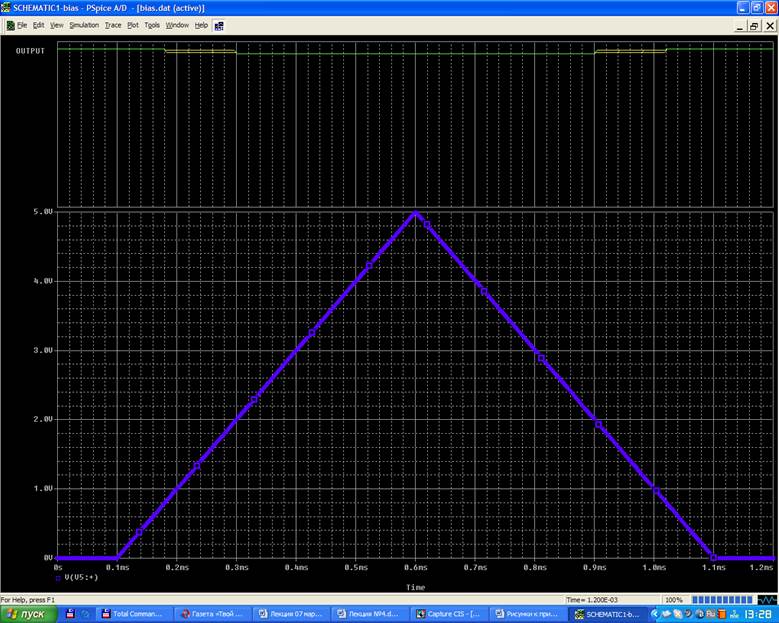

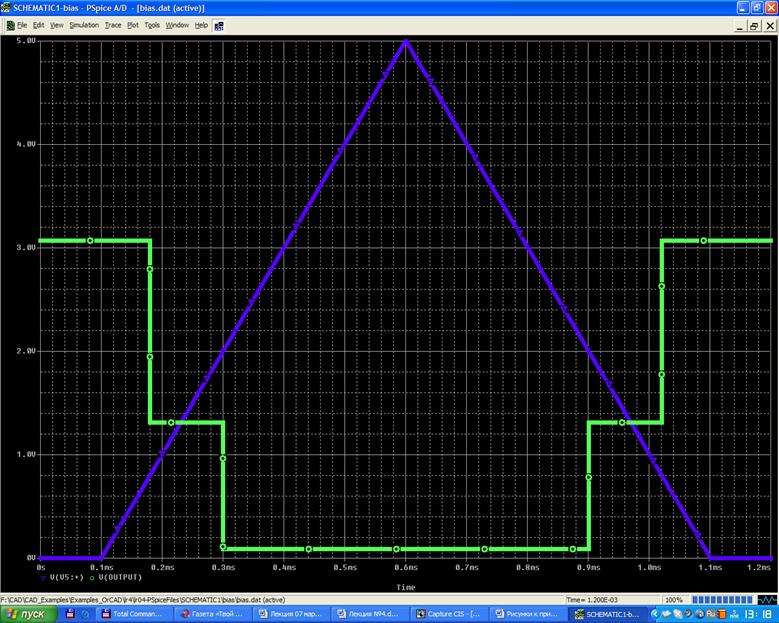

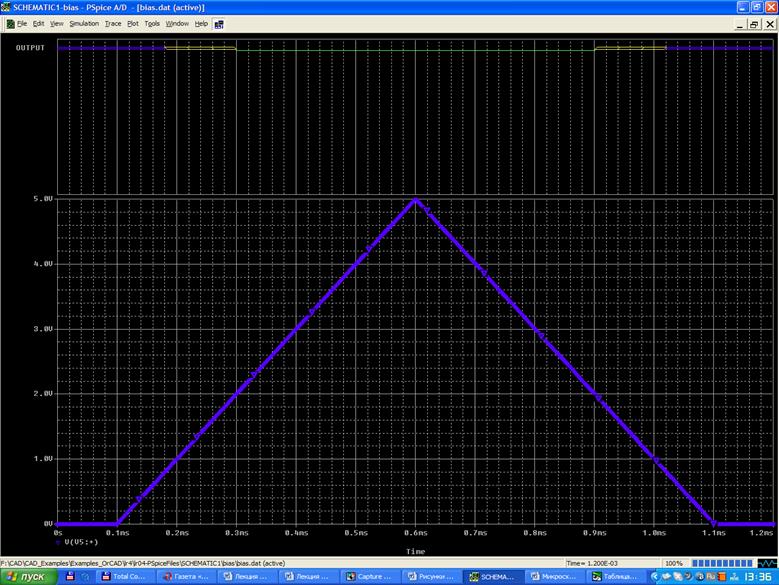

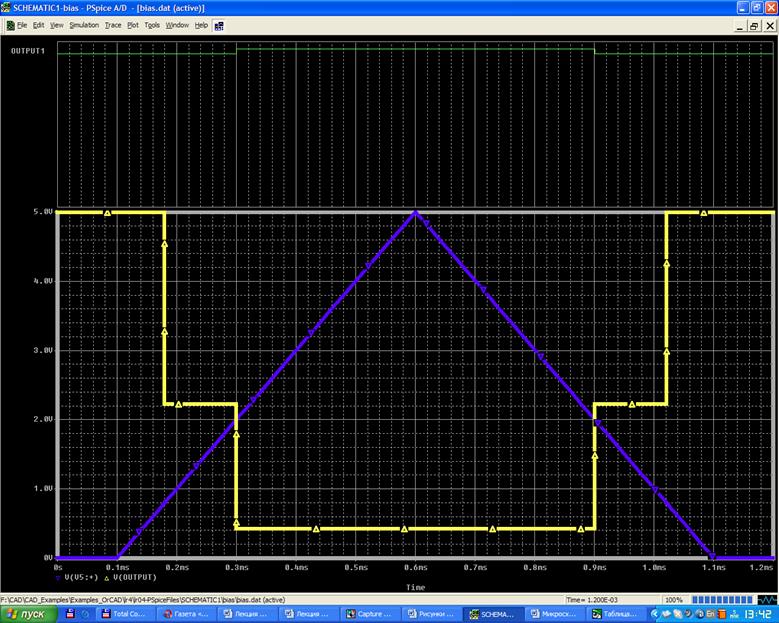

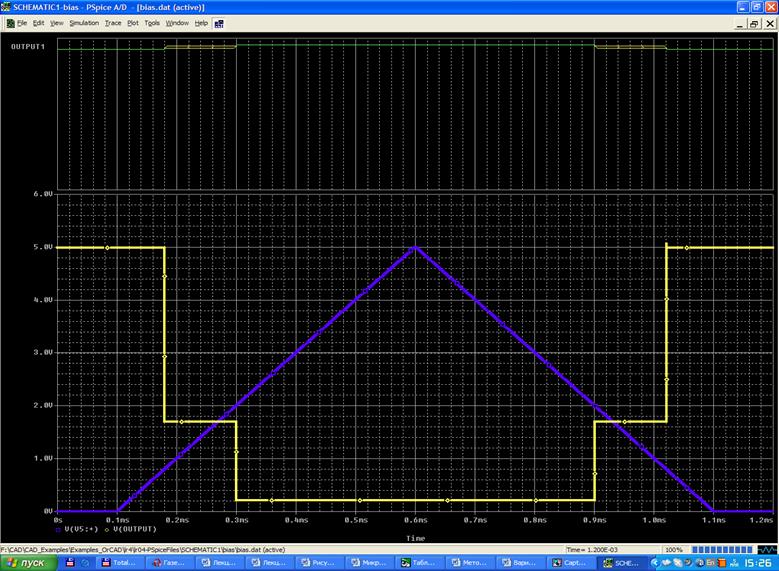

На вход схемы инвертора подаётся линейно-изменяющиеся напряжение от 0 до 5В (параметру PW не рекомендуется присваивать 0В!, он должен быть близок нулю). На графике состояния выхода инвертора видно, каким напряжениям соответствует логические состояния микросхем. Например, при Uвх в диапазоне от 0.8В до 2.0В схема находится в неопределённом состоянии, что индицируется двойной жёлтой линией.

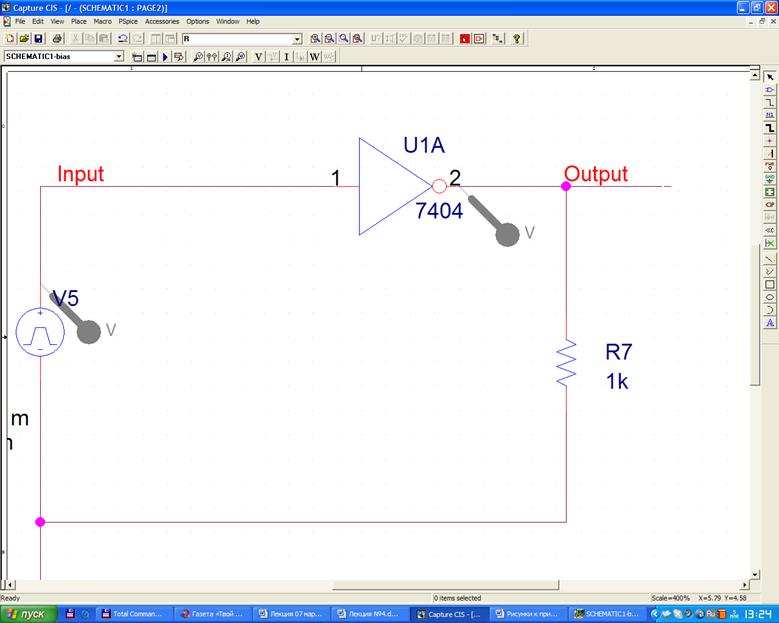

Подключив на выход микросхемы высокоомный резистор, можно определить значение напряжения на выходе микросхемы при входном напряжении в диапазоне от 0.8В до 2.0В, т.е. когда её вход находится в неопределённом состоянии.

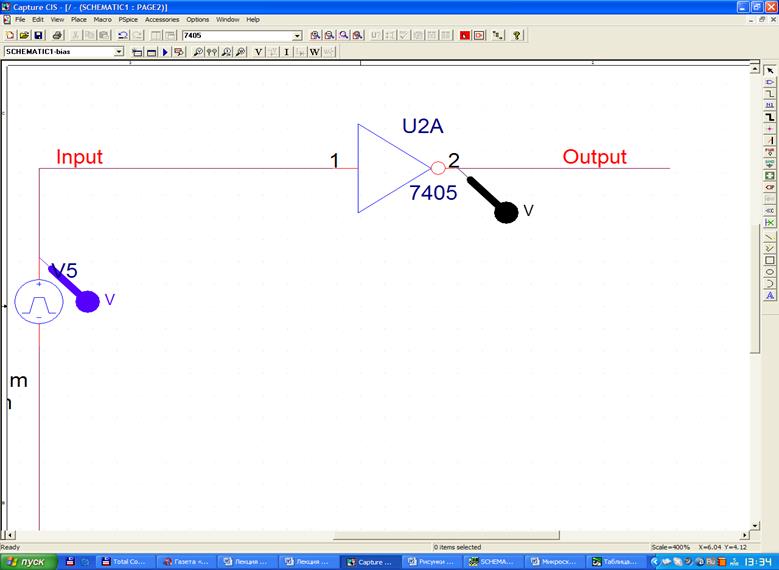

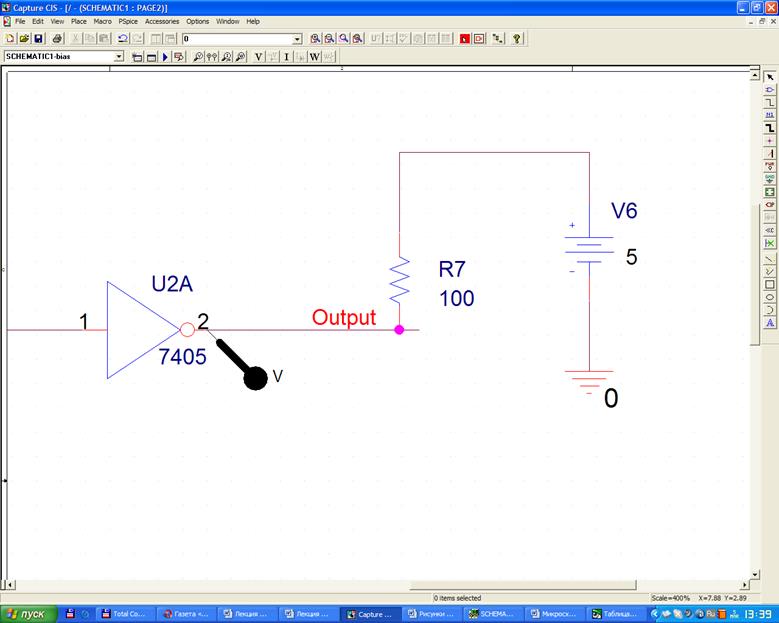

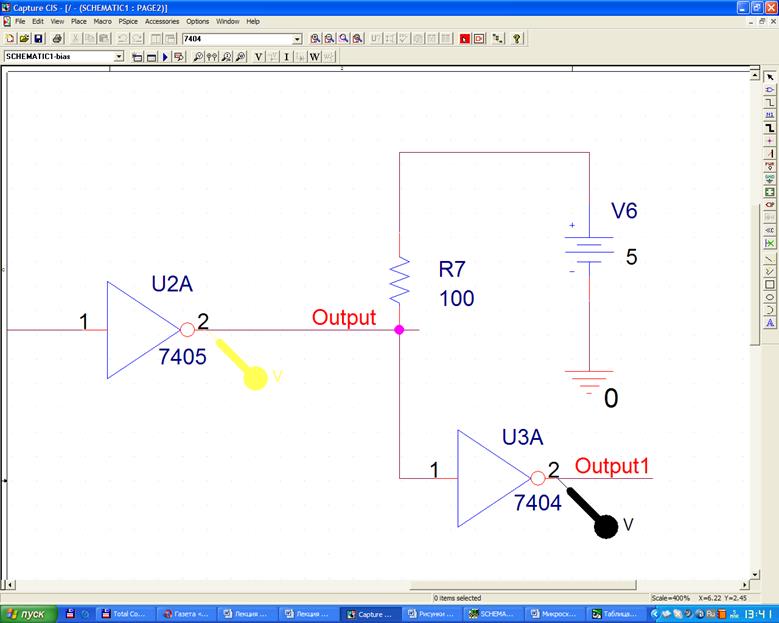

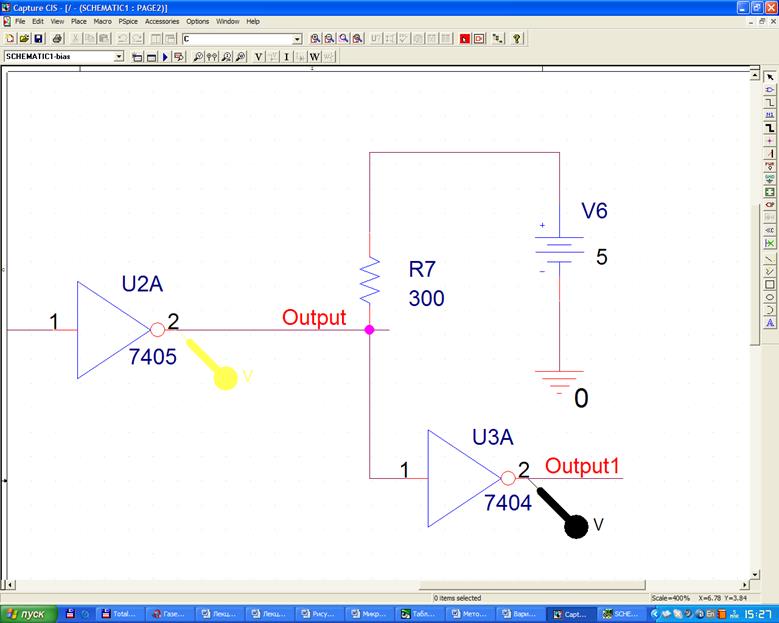

2 Моделирование схем с открытым коллектором

В схеме с открытым коллектором вместо логического ноля мы видим высокоимпедасное состояние.

На приведённом выше рисунке к выходу микросхемы подключён резистор, после чего схема приведена в работоспособное состояние, что можно проверить на простом примере. Варьируя значением сопротивления можем добиться различных напряжений на выходе микросхемы с открытым коллектором при переходе её в неопределённое состояние.

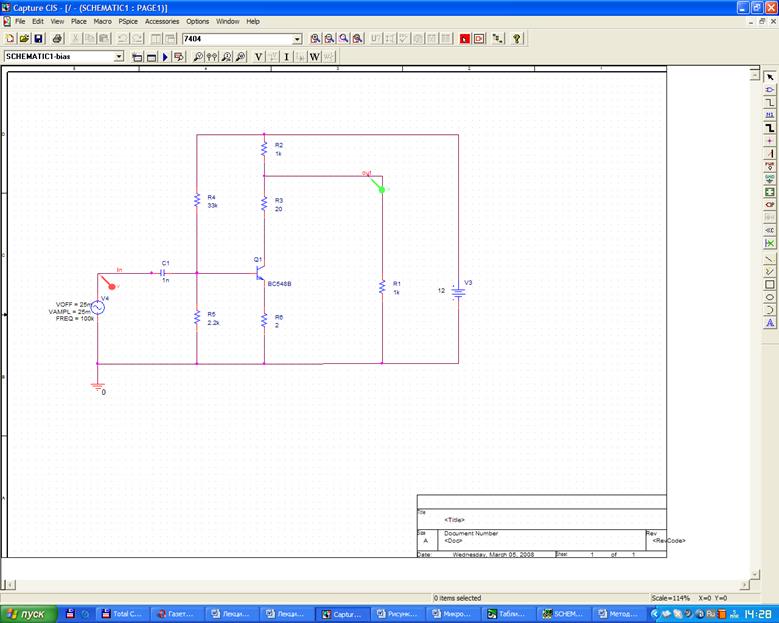

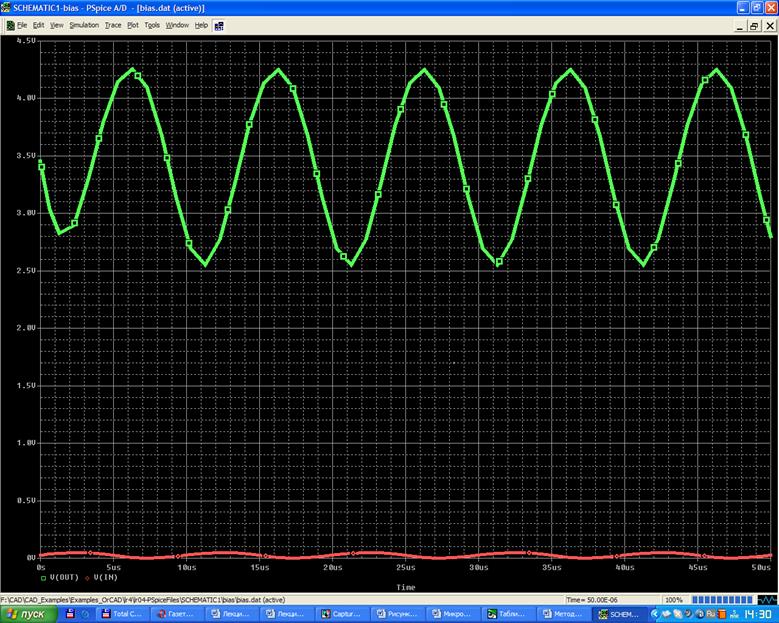

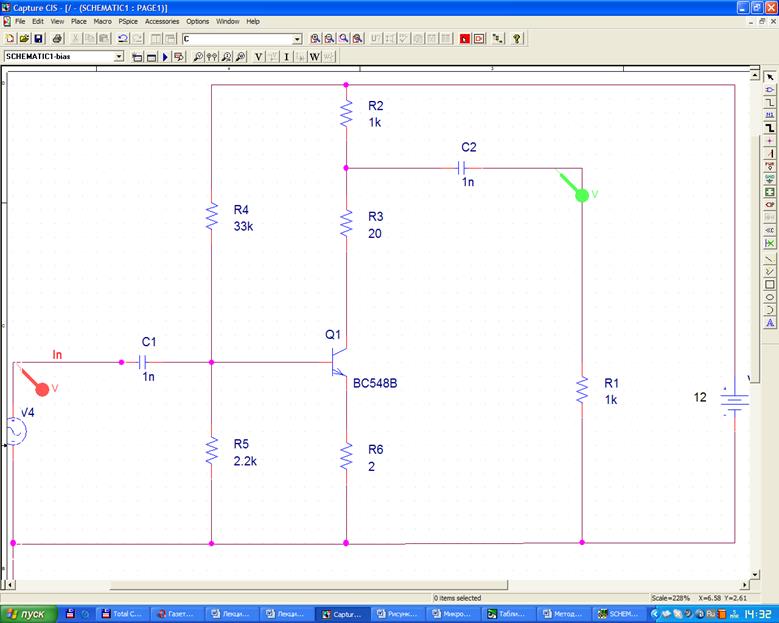

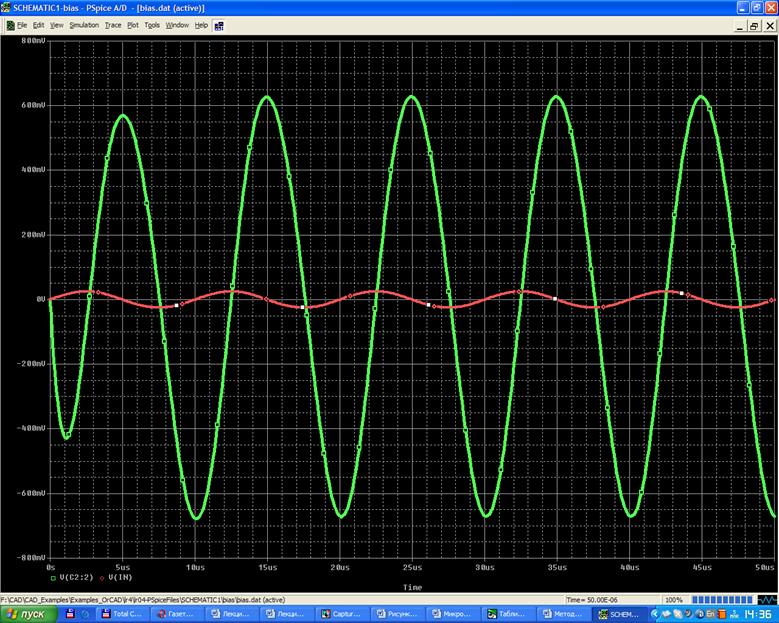

3 Моделирование схемы транзисторного усилителя

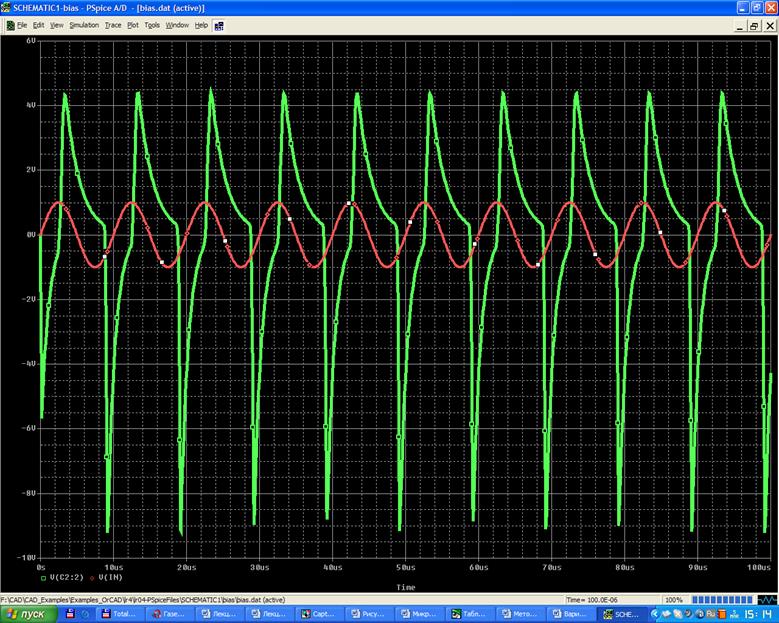

4 Характер переходного процесса при амплитуде входного сигнала 1В

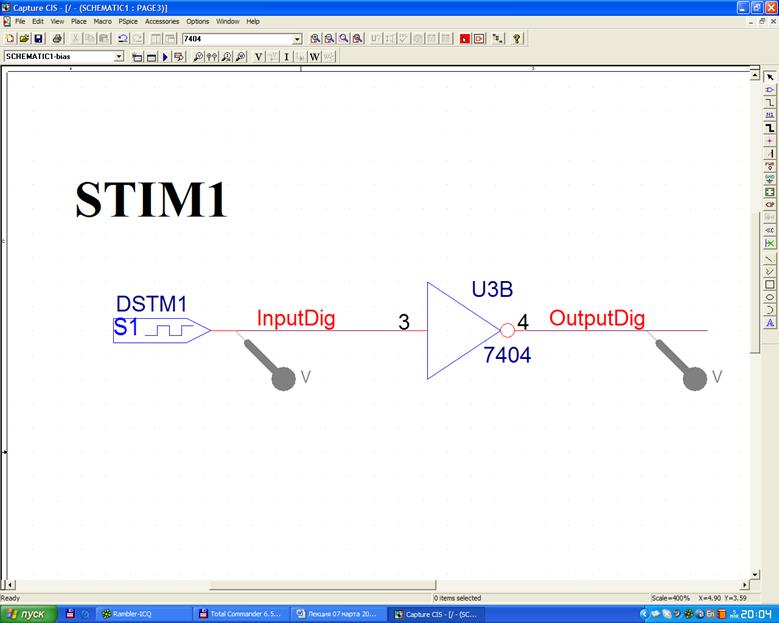

5 Цифровое динамическое моделирование

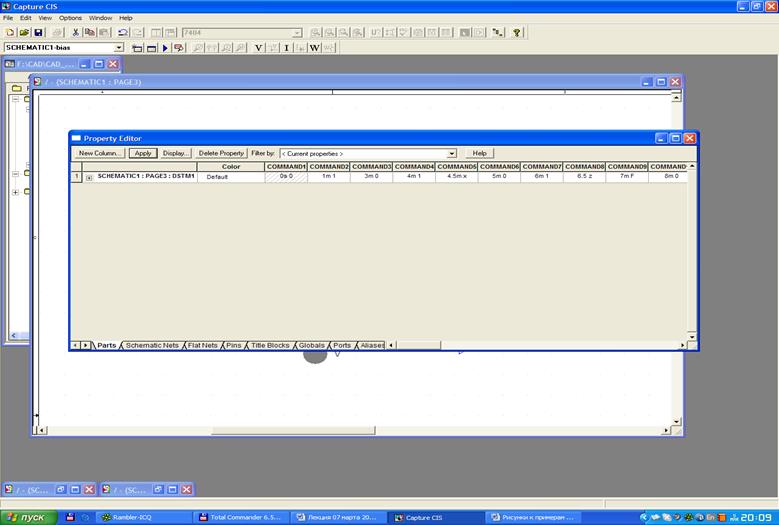

Пример задания атрибутов генератора цифровых сигналов

U_DSTM1 STIM(1,1)

+ $G_DPWR $G_DGND

+ INPUTDIG

+ IO_STM

+ IO_LEVEL=0

+ 0s 0

+ 1m 1

+ 3m 0

+ 4m 1

+ 4.5m x

+ 5m 0

+ 6m 1

+ 6.5m z

+ 7m F

+ 8m 0

+ 9m R

+ 10m 1

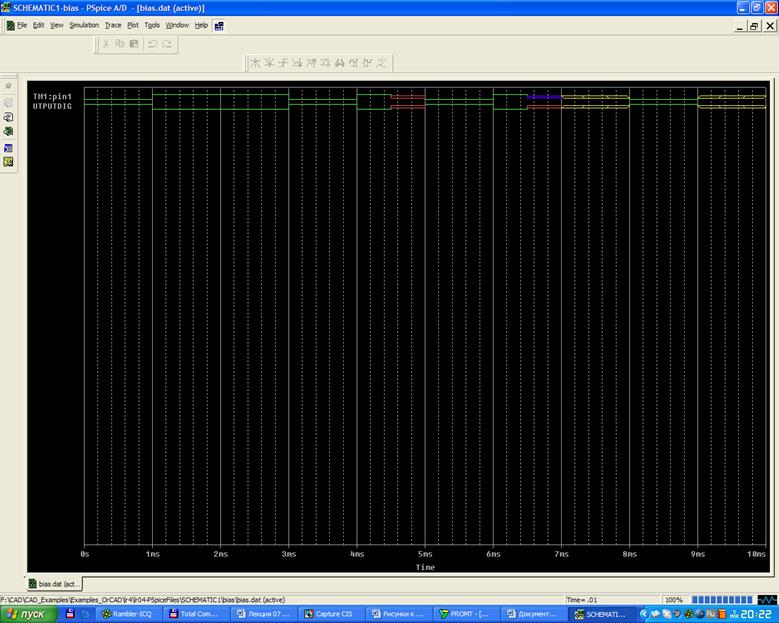

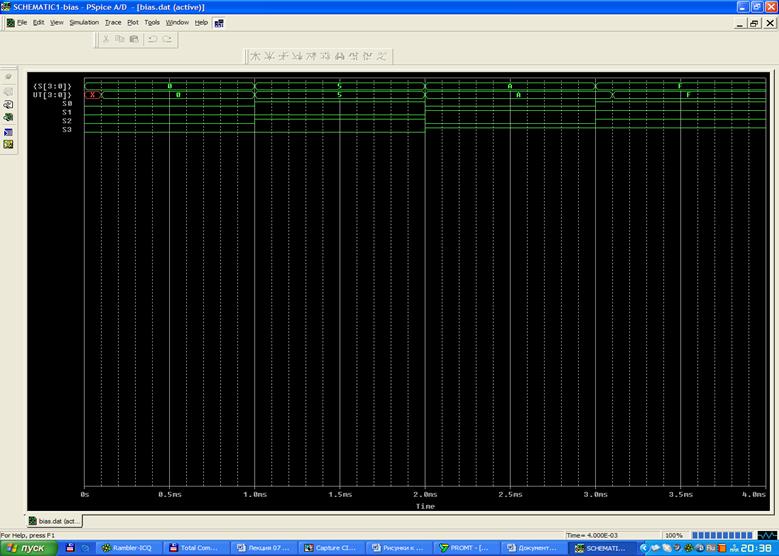

Эпюры логических состояний входа и выхода схемы при изменении задании входной цифровой последовательности в соответствии с приведённым выше примером.

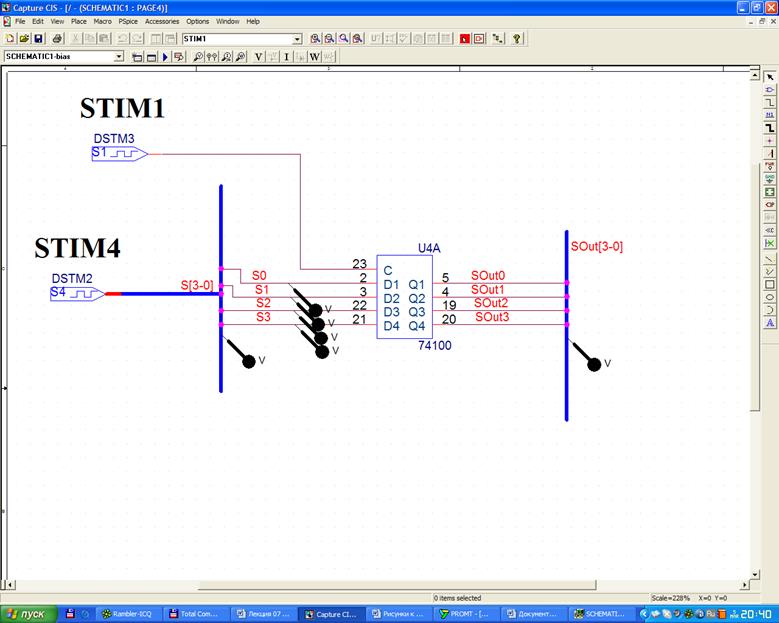

Пример использования генератора с 4-мя цифровыми выходами

Следует обратить внимание на то, что пакет позволяет индицировать как состояние шины, так и отдельных её проводников. Каждый проводник, который подходит и/или отходит от шины должен быть подписан. В противном случае, очевидно, пакет не сможет идентифицировать какой из проводников к какому входу или выходу микросхемы подключён.

Метки и шины подписываются при помощи опции «Place net alias», вынесенной в виде иконки на правую переднюю панель.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.