Лабораторная работа №3

Вполнил студент группы эт-31 Быховский А.А.

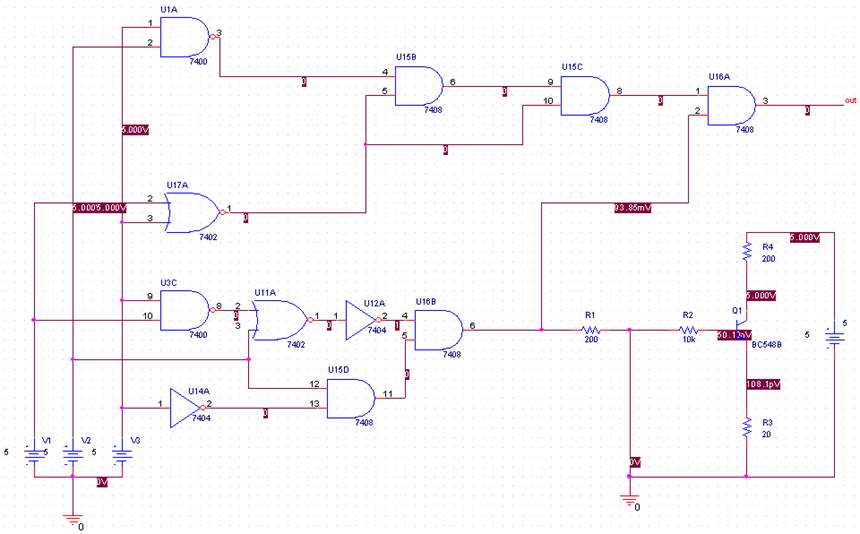

Анализ цифровых и цифро-аналоговых схем в пакете OrCAD

Цель работы: Овладеть навыками анализа цифровых и цифро-аналоговых цепей в пакете OrCAD

1.

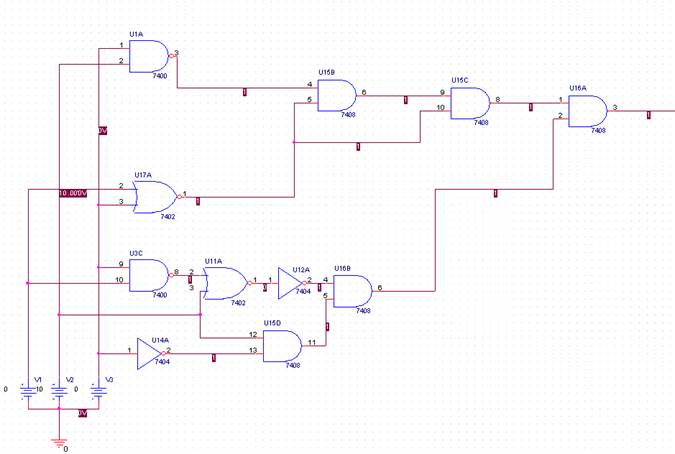

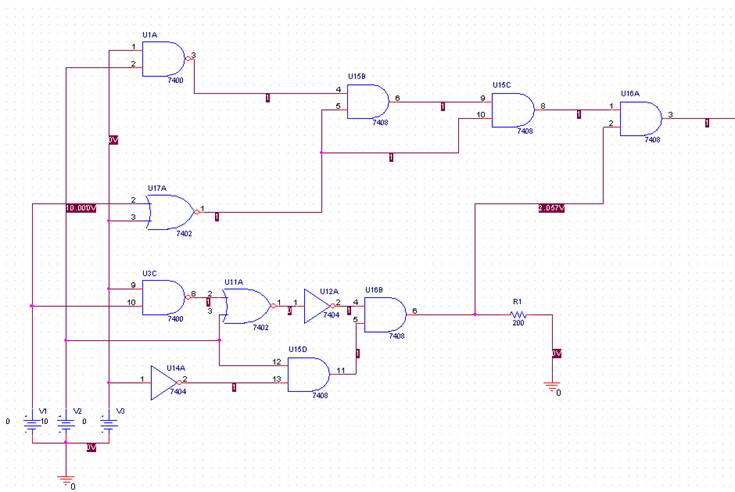

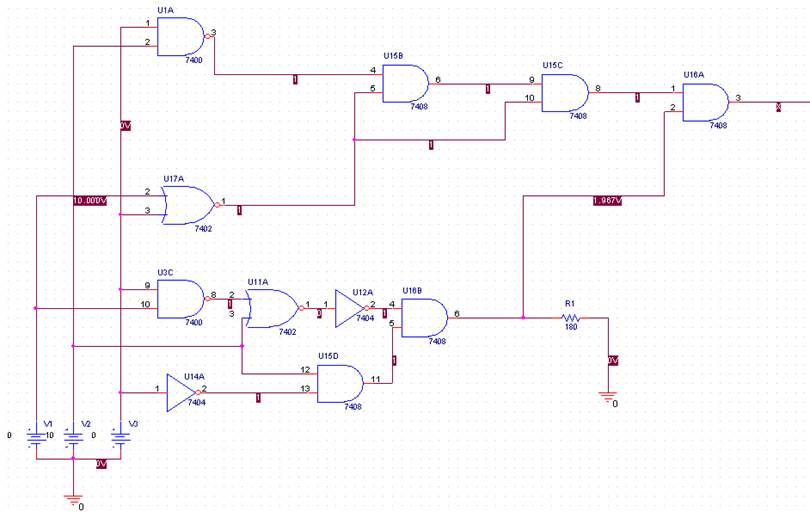

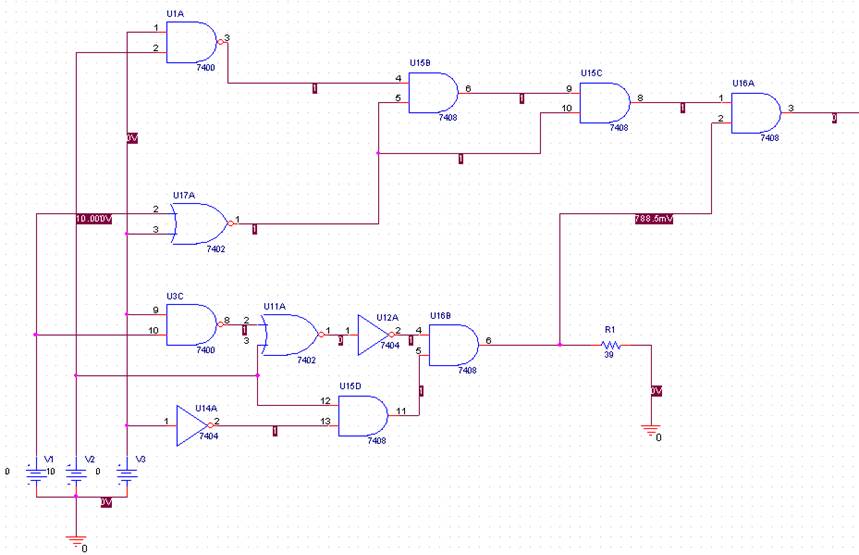

Подавая на вход цепи

различные комбинации входных сигналов от источников постоянного напряжения,

выполнили моделирование схемы – анализ переходных процессов.

Рис.1

Рис.2

Рис.3

Рис.4

Рис.4

Рис.5

Распечатаем и выполним анализ файла описания схемы (файла *.OUT)

**** 03/14/07 15:04:46 ******* PSpice 10.5.0 (Jan 2005) ******* ID# 2089878865

** Profile: "SCHEMATIC1-bias" [ F:\WorksAlek\MATMOD\2S\L3\lab_3-pspicefiles\schematic1\bias.sim ]

**** CIRCUIT DESCRIPTION

******************************************************************************

** Creating circuit file "bias.cir"

** WARNING: THIS AUTOMATICALLY GENERATED FILE MAY BE OVERWRITTEN BY SUBSEQUENT SIMULATIONS

*Libraries:

* Profile Libraries :

* Local Libraries :

* From [PSPICE NETLIST] section of C:\OrCAD\OrCAD_10.5\tools\PSpice\PSpice.ini file:

.lib "nom.lib"

*Analysis directives:

.TRAN 0 1000ns 0

.PROBE V(alias(*)) I(alias(*)) W(alias(*)) D(alias(*)) NOISE(alias(*))

.INC "..\SCHEMATIC1.net"

**** INCLUDING SCHEMATIC1.net ****

* source LAB_3

X_U11A N01644 N05107 N01692 $G_DPWR $G_DGND 7402 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U15B N00858 N01251 N01081 $G_DPWR $G_DGND 7408 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U16A N01134 N03653 OUT $G_DPWR $G_DGND 7408 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U14A N05031 N05596 $G_DPWR $G_DGND 7404 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U1A N05031 N05107 N00858 $G_DPWR $G_DGND 7400 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

R_R4 N19324 N19654 200

X_U12A N01692 N01743 $G_DPWR $G_DGND 7404 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

V_5 N19654 0 5

X_U15C N01081 N01251 N01134 $G_DPWR $G_DGND 7408 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U17A N05186 N05031 N01251 $G_DPWR $G_DGND 7402 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

R_R2 0 N19252 10k

Q_Q1 N19324 N19252 N19470 BC548B

V_V1 N05186 0 5

X_U15D N05107 N05596 N10631 $G_DPWR $G_DGND 7408 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U3C N05031 N05186 N01644 $G_DPWR $G_DGND 7400 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U16B N01743 N10631 N03653 $G_DPWR $G_DGND 7408 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

V_V2 N05107 0 5

R_R3 0 N19470 20

R_R1 N03653 0 200

V_V3 N05031 0 5

**** RESUMING bias.cir ****

.END

**** Generated AtoD and DtoA Interfaces ****

*

* Analog/Digital interface for node N05186

*

* Moving X_U3C.U1:IN2 from analog node N05186 to new digital node N05186$AtoD

X$N05186_AtoD1

+ N05186

+ N05186$AtoD

+ $G_DPWR

+ $G_DGND

+ AtoD_STD

+ PARAMS: CAPACITANCE= 0

* Moving X_U17A.U1:IN1 from analog node N05186 to new digital node N05186$AtoD2

X$N05186_AtoD2

+ N05186

+ N05186$AtoD2

+ $G_DPWR

+ $G_DGND

+ AtoD_STD

+ PARAMS: CAPACITANCE= 0

*

* Analog/Digital interface for node N05107

*

* Moving X_U15D.U1:IN1 from analog node N05107 to new digital node N05107$AtoD

X$N05107_AtoD1

+ N05107

+ N05107$AtoD

+ $G_DPWR

+ $G_DGND

+ AtoD_STD

+ PARAMS: CAPACITANCE= 0

* Moving X_U1A.U1:IN2 from analog node N05107 to new digital node N05107$AtoD2

X$N05107_AtoD2

+ N05107

+ N05107$AtoD2

+ $G_DPWR

+ $G_DGND

+ AtoD_STD

+ PARAMS: CAPACITANCE= 0

* Moving X_U11A.U1:IN2 from analog node N05107 to new digital node N05107$AtoD3

X$N05107_AtoD3

+ N05107

+ N05107$AtoD3

+ $G_DPWR

+ $G_DGND

+ AtoD_STD

+ PARAMS: CAPACITANCE= 0

*

* Analog/Digital interface for node N03653

*

* Moving X_U16A.U1:IN2 from analog node N03653 to new digital node N03653$AtoD

X$N03653_AtoD1

+ N03653

+ N03653$AtoD

+ $G_DPWR

+ $G_DGND

+ AtoD_STD

+ PARAMS: CAPACITANCE= 0

* Moving X_U16B.U1:OUT1 from analog node N03653 to new digital node N03653$DtoA

X$N03653_DtoA1

+ N03653$DtoA

+ N03653

+ $G_DPWR

+ $G_DGND

+ DtoA_STD

+ PARAMS: DRVH= 96.4 DRVL= 104 CAPACITANCE= 0

*

* Analog/Digital interface for node N05031

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.