|

№ |

Метка |

Команды |

Комментарии |

||||||

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 |

PUSH B PUSH H PUSH PSW IN F5 CMA ANI 01 (H) MOV B,A LDA 21FD (H) ORA B LHL D 21FB ORA L MOV L,A MOV A,M MOV B,A LDA 21FD (H) ORA B CMA OUT F4 POP PSW POP H POP B RET |

Сохранение регистров B, C, H, L, PSW в стеке Ввод X→D0 аккумулятора А Инверсия А Выделение разряда D0 Сохранение Х в регистре В Чтение текущего состояния автомата Si Логическое сложение Si и Х 20(H)→L; 22h→H

Формирование младшего байта адреса выходной функции Z Чтение выходной функции Z Сохранение Z в регистре В Чтение состояния Si Логическое сложение Z и Si Инверсия выходного вектора Вывод выходного вектора в порт А

Восстановление регистром B, C, H, L, PSW Возврат в программу TABLE |

Рис. 13

Рис. 14

|

S\X |

0 |

1 |

|

1 |

2 2 2 2 |

2 2 2 3 |

|

2 |

2 2 2 4 |

2 2 2 5 |

|

3 |

2 2 2 6 |

2 2 2 7 |

|

4 |

2 2 2 8 |

2 2 2 9 |

|

5 |

2 2 2 A |

2 2 2 B |

|

6 |

2 2 2 C |

2 2 2 D |

Таблица 6

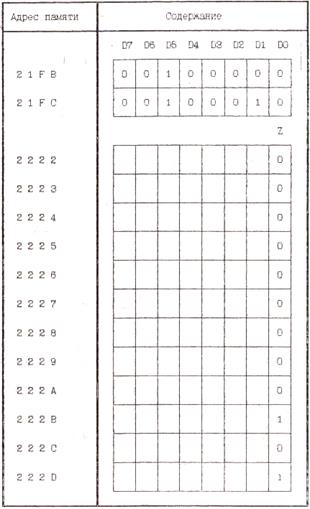

В табл.6 в клетках проставлены адреса ячеек памяти, в которых содержится значение выходной функции 2.

Рассмотрим работу подпрограммы VF после выполнения подпрограммы SI, когда автомат переходит в состояние 2 и в ячейки 21FD (Н) записан байт 00000100.

После вызова подпрограммы СА11 VF осуществляется пересылка содержимого регистров Н, I, PSW в стек и вводится входной набор х = 1. При этом в регистре В формируется байт 00000001. Затем производится логическое сложение байта входного набора и байта внутреннего состояния автомата Si (00000001 v 00000010 = 00000011 = 03(Н)). В регистровой паре HL формируется адрес 2223(Н) (см.рис.13 и табл.6 ) ячейки памяти, откуда считывается код выходной функции Z(00000000) и сохраняется в регистре В. Затем логически складывается байт состояния автомата Z(00000100) и байт выходной функции Z(00000000). Результатом сложения будет выходной вектор (00000100), в разряде D0 которого находится выходная функция автомата Z = 0 , а в разрядах D3,D2,D1 код 010 - двоичное представление состояния Si=2. Далее выходной вектор выводится в канал А ППА, производится восстановление регистров и возврат в программу TABLE.

Рассмотренный способ программной реализации автомата является интерпретирующим. Настройка на определенный автомат осуществляется указанием соответствующего базового адреса и введением карт памяти констант. Обработка различных автоматов может осуществляться последовательно во времени без внешних сигналов прерывания .

Недостатком данного способа, по сравнению со способом программной реализации автомата по графу переходов, является снижение быстродействия программы.

4. ПРОГРАММНАЯ РЕАЛИЗАЦИЯ АВТОМАТА ПУТЕМ ВЫЧИСЛЕНИЯ БУЛЕВЫХ ФУНКЦИЙ

Программная реализация автомата по булевым функциям предполагает, что построение блок-схемы программы происходит по структурной схеме автомата Мили 1 рода (рис. 14). Только структурная схема показывает, почему не происходит мгновенной передачи значений Y1(t),Y2(t)Y3(t) на вход логического преобразователя (ЛП) и, следовательно, исключаются критические состязания. Очевидно, что эта особенность должна быть учтена на блок-схеме алгоритма автомата.

Рис. 15

На рис.15 показана блок-схема алгоритма программы автомата, использующая вычисление булевых функций, а на рис.16 приведена соответствующая ей программа BF на ассемблере. Следует отметить, что при построении табл.3 не решалась задача исключения критических состязаний, т.к. предполагалось, что блок-схема алгоритма автомата по методу вычисления булевых функций будет реализована, как синхронный автомат. На структурной схеме автомата (см. рис.14) задачи исключения критических состязаний решаются следующим образом: вычисленные в ЛП новые значения Y1(t),Y2(t),Y3(t) по линиям обратных связей поступают на вход ЛП не сразу, а задерживаются в блоке памяти (БП), тем самым снимая проблему критических состязаний [C].

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.