5. Увеличено число сигналов логического воздействия на микроЭВМ.

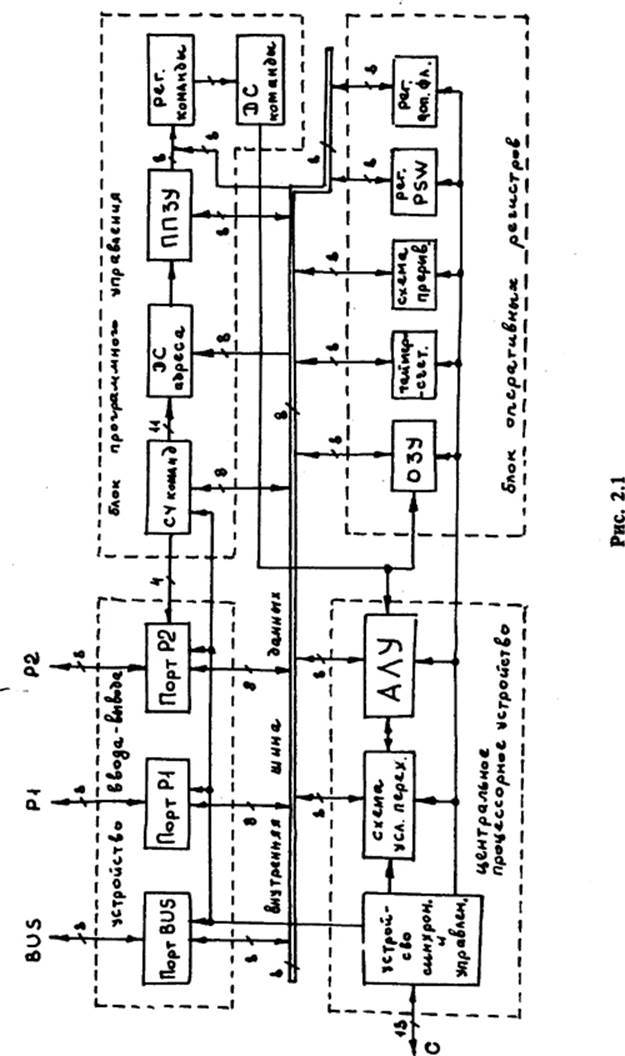

Элементы структурной схемы могут быть объединены в четыре блока (обведены пунктирной линией):

Центральное процессорное устройство включает в себя устройство синхронизации и управления, АЛУ и схему условных переходов, которая организует условные переходы по битам регистра флажков АЛУ и внешним сигналам управления ТО и Т1. АЛУ строится аналогично МП580 — оно выполняет операции накапливающего типа в двоичной и десятичной арифметике [2].

Устройство синхронизации и управления связано с периферийными устройствами 13-разрядной шиной С {12: 0}, отдельные провода которой несут на себе следующие сигналы (в скобках указаны аналоги сигналов МП580):

BQ1, BQ2 - подключение кварца или LC — цепи синхронизации встроенного тактового генератора или входа внешнего тактового генератора;

WR (WR) — запись во внешнюю память данных, запись из порта BUS во внешнее устройство;

RD (DBIN) — чтение из внешней памяти или из внешних устройств, подключенных к порту BUS

ALE (C) (address latch enable) — стробирование внешней памяти;

SR (RESET) (set-reset) - инициализация микроЭВМ;

INT (INT) — сигнал запроса на прерывание;

SS — организация пошагового выполнения программы (используется совместно с ALE);

PME (periphery memory enable) - стробирование внешней памяти при чтении;

EMA (external memory access} — доступ к внешней памяти. Используется также при программировании и проверке ППЗУ; PR (periphery register) — расширение каналов ввода/вывода. Используется также при программировании ППЗУ; ТО — ввод условия для JTO/JNTO или выход тактовых сигналов после выполнения команды ENTO CLK; TI — ввод условия для JT1/JNT1 или ввод счетчика внешних событий после выполнения команды STRT CNT.

Блок программного управления преобразует коды команд программы в сигналы управления. Он включает в себя счетчик команд (PC), дешифратор адреса команды, ППЗУ, регистр команды (IR) и дешифратор команды (IDC). В отличие от МП580, этот блок может работать как с внутренней, так и с внешней памятью. В последнем случае код адреса РС {11 : 0} подается на внешнюю программную память, а байтный код команды записывается непосредственно в регистр команды.

Устройство ввода/вывода включает в себя три байтных порта BUS, PI и Р2. Порты Р\ и Р2 имеют идентичные характеристики. При выводе информации данные от ЭВМ записываются в регистры порта и остаются там неизменными до следующей записи.

При вводе информации входной код, поддерживаемый неизменным на время действия импульса RD, маскируется кодом регистра порта и передается в микроЭВМ. Если код вводится без изменений, предварительно, еще до ввода, в регистре порта должен быть записан единичный код маски. Записанный в режиме вывода код регистра порта может программно модифицироваться.

Порт Р2 используется также для подключения расширителя ввода/вывода и выдачи четырех старших разрядов программного счетчика РС{11 : 8 }.

Порт BUS реализует двунаправленный канал передачи данных. Он передает восемь младших разрядов кода адреса команд РС{1 : 0} или кода адреса данных ADRD {7 : 0} при работе с внешней программной памятью или памятью данных и байт данных D{1 : 0} при работе с внешней памятью или схемами расширения (интерфейсные БИС серии К580). По завершению передачи данных порт переходит в третье состояние.

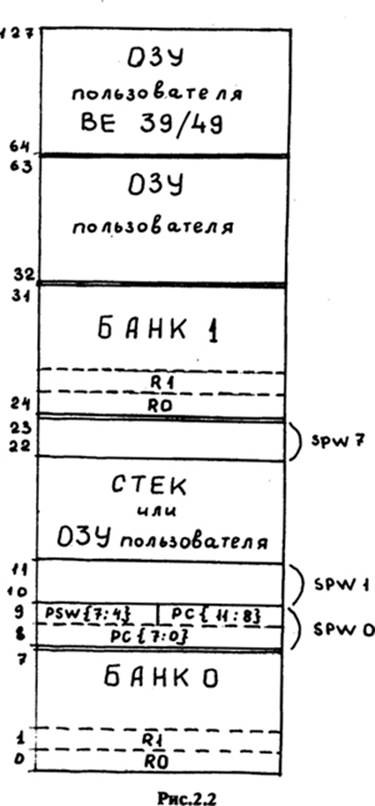

Блок оперативных регистров включает в себя ОЗУ, таймер-счетчик, регистр состояния

программы, схему прерывания и регистр дополнительных

флажков. Оперативное запоминающее устройство имеет объем либо в 64 байта (BE

35/48 ), либо 128 байт (BE 39/49). Назначение отдельных ячеек ОЗУ изображено на

рис. 2.2.

программы, схему прерывания и регистр дополнительных

флажков. Оперативное запоминающее устройство имеет объем либо в 64 байта (BE

35/48 ), либо 128 байт (BE 39/49). Назначение отдельных ячеек ОЗУ изображено на

рис. 2.2.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.