Государственное образовательное учреждение

высшего профессионального образования

“петербургский государственный университет путей сообщения

министерства путей сообщения Российской Федерации”

Кафедра «Радиотехника»

В.К.Фунзавя

Т.М Родигина

В.В.Шматченко

Методические указания к выполнению лабораторной работы №9

«ИССЛЕДОВАНИЕ ТРАНЗИСТОРНОГО КЛЮЧА»

Санкт-Петербург

2005

1. Цель работы: Исследование работы транзисторного ключа на биполярном транзисторе.

Задачи:

1. Определение по передаточной характеристике логического перепада и помехоустойчивости транзисторного ключа.

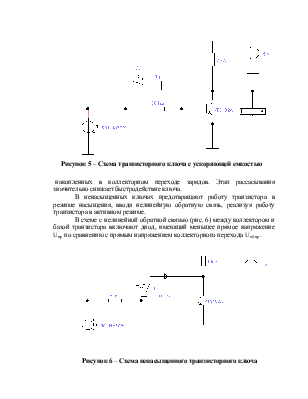

2. Исследование методов повышения быстродействия насыщенного ключа, за счет ускоряющей емкости.

3. Исследование работы транзисторного ключа в ненасыщенном режиме.

2. Краткие сведения из теории

2.1. Транзисторный ключ предназначен для замыкания и размыкания цепи нагрузки под воздействием управляющих импульсов входного сигнала. Он также является основным базовым элементом импульсных и цифровых устройств.

В статическом режиме ключевая схема находится либо в состоянии «включено» (ключ замкнут), либо в состоянии «выключено» (ключ разомкнут).

Переключение ключевой схемы из одного состояния в другое осуществляется благодаря воздействию на нее входного управляющего сигнала имеющего форму импульса или уровней напряжений: соответственно низкого, обозначаемого U0, и высокого, обозначаемого U1.

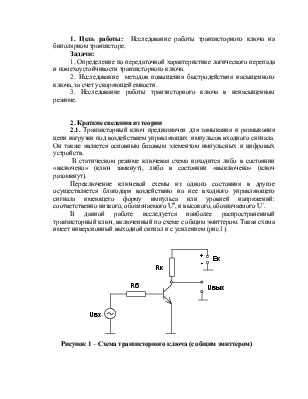

В данной работе исследуется наиболее распространенный транзисторный ключ, включенный по схеме с общим эмиттером. Такая схема имеет инверсионный выходной сигнал и с усилением (рис.1).

|

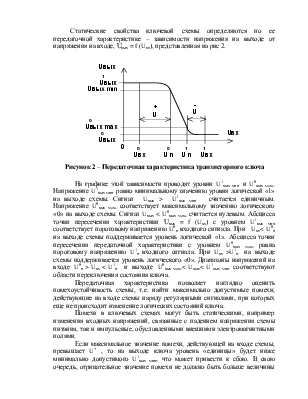

Статические свойства ключевой схемы определяются по ее передаточной характеристике – зависимости напряжения на выходе от напряжения на входе, Uвых = f (Uвх), представленная на рис 2.

На графике этой зависимости проводят уровни U1вых мин и U0вых макс. Напряжение U1вых мин равно минимальному значению уровня логической «1» на выходе схемы. Сигнал Uвых > U1вых мин считается единичным. Напряжение U0вых макс соответствует максимальному значению логического «0» на выходе схемы. Сигнал Uвых < U0вых макс считается нулевым. Абсцисса точки пересечения характеристики Uвых = f (Uвх) с уровнем U1вых мин соответствует пороговому напряжению U0п входного сигнала. При Uвх< U0п на выходе схемы поддерживается уровень логической «1». Абсцисса точки пересечения передаточной характеристики с уровнем U0вых макс равна пороговому напряжению U1п входного сигнала. При Uвх >U1п на выходе схемы поддерживается уровень логического «0». Диапазоны напряжений на входе U0п > Uвх < U1п и выходе U0вых макс< Uвых< U1вых мин соответствуют области переключения состояния ключа.

Передаточная характеристика позволяет наглядно оценить помехоустойчивость схемы, т.е. найти максимально допустимые помехи, действующие на входе схемы наряду регулярными сигналами, при которых еще не происходит изменение логических состояний ключа.

Помехи в ключевых схемах могут быть статическими, например изменения входных напряжений, связанные с падением напряжения схемы питания, так и импульсные, обусловленными внешними электромагнитными полями.

Если максимальное значение помехи, действующей на входе схемы, превышает U+ , то на выходе ключа уровень «единицы» будет ниже минимально допустимого U1вых мин, что может привести к сбою. В свою очередь, отрицательное значение помехи не должно быть больше величины U− . Величины U+ и U− характеризуют помехоустойчивость ключа. Они должны быть по возможности большими. Разность номинальных уровней входных напряжений логических единицы и нуля называют логическим перепадом

Uлп = U1вх – U0вх = (U1п + U−) – (U0п - U+ ) = (U1п - U0п) + (U+ +U−) (1)

Как видно из выражения, допустимые значения U+ и U− будут наибольшими при совпадении пороговых значений, т.е. при U1п = U0п . Тогда

Uлп = U+ + U− (2)

2. Быстродействие схемы транзисторного ключа.

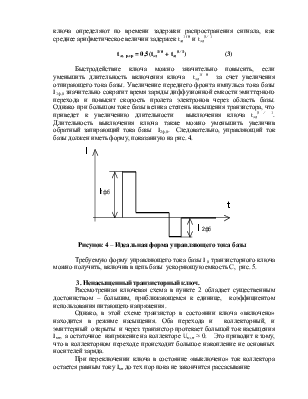

Одной из важнейших динамических характеристик ключевой схемы является ее быстродействие, т.е. высокая скорость перехода ключа из одного состояния в другое. Такой переход не может быть мгновенным из-за переходных процессов происходящих в транзисторе, в частности, из-за влияния диффузионных емкостей эмиттерного и коллекторного переходов и временем пролета электронов через область базы. На рис. 3 приведены временные диаграммы входного и выходного напряжений ключевой схемы.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.