МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ

НАЦІОНАЛЬНИЙ ТЕХНІЧНИЙ УНІВЕРСИТЕТ

“ХАРКІВСЬКИЙ ПОЛІТЕХНІЧНИЙ ІНСТИТУТ”

КАФЕДРА ОБЧИСЛЮВАЛЬНОЇ ТЕХНІКИ ТА ПРОГРАМУВАННЯ

Лабораторна робота №6

по курсу “Комп’ютерна схемотехніка”

Виконав:

cтудент гр. КІТ-14в

«» Заразилов Д.I.

Перевірив:

«» Рисований О.М.

Хуторенко С.В.

Ціль роботи: ознайомлення з роботою прямокутного дешифратора “1 з 16” з інверсними виходами.

Дослід 1. Дослід дешифратора у статичному режимі роботи.

Ціль: Дослідити роботу дешифратора у статичному режимі роботи, надбання навичок у створенні макросів засобами пакета Electronics Workbench.

Проведення досліду.

1. Зібрати дві ступіні дешифратора.

2. Створити їх макроси.

3. З’єднати макроси в дешифратор.

4. Протестувати дешифратор в статичному режимі.

5. Побудувати таблицю станів та часові діаграми.

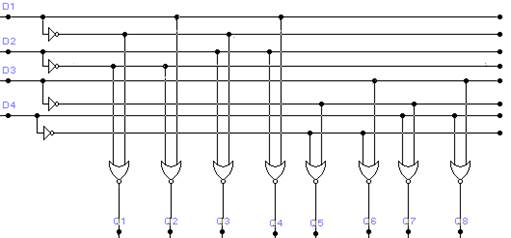

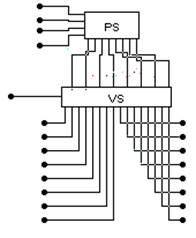

На рис. 1.1. показана схема першої ступіні дешифратора.

D1..D4 – інформаційні входи;

Q1..Q4 – виходи на другу ступінь;

Виділимо отриману схему та за допомогою команд меню Circuit-Subcircuit отримаємо макрос схеми, який назвемо PS.

Рис. 1.2. Макрос першої ступіні дешифратора

Положення виводів макроса відповідає положенню виводів схеми.

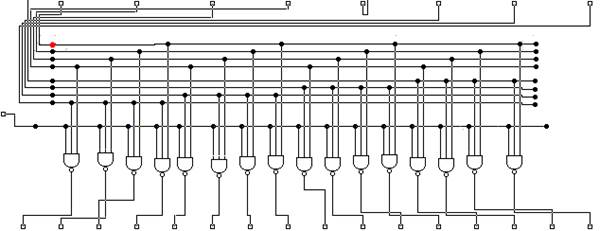

Тепер зберемо другу ступінь дешифратора. Схема другої ступіні наведена на рис. 1.3.

Рис. 1.3. Схема другої ступіні дешифратора.

D1..D8 – входи з першої ступіні;

Q1..Q16 – виходи дешифратора;

Е – вхід синхронізації.

Для цієї схеми отримаємо макрос, який назвемо VS:

Рис. 1.4. Макрос другої ступіні дешифратора.

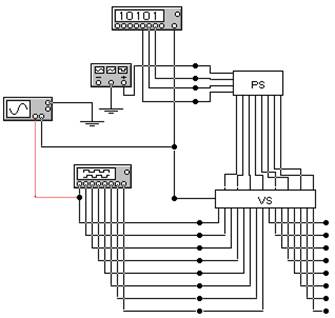

Об’єднаємо обидві ступіні в дешифратор. Схему дешифратора наведено на рис. 1.5.

Рис. 1.5. Схема декодера.

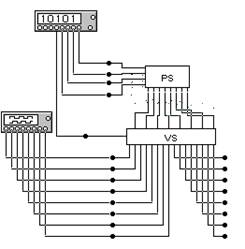

На рис. 1.6. наведено схему проведення досліду.

Рис. 1.6. Схема проведення досліду 1

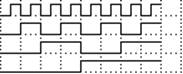

Дослідимо роботу дешифратора. За допомогою генератора слів подамо на входи дешифратора послідовності 0000-1111, а на вхід синхронізації – 1. Заміряємо логічним аналізатором рівні сигналів на виходах ступіні PS та на виході 4 дешифратора для всіх комбінацій.

|

![]()

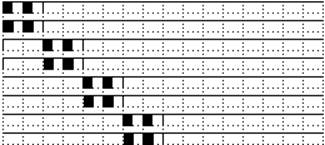

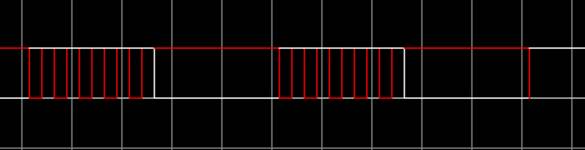

Рис. 1.7. Часові діаграми роботи дешифратора

Як бачимо, перша ступінь дешифратора працює теж як двоступеневий дешифратор – при подачі на входи війкового 4-значного коду на виходи Q1..Q4 подається унітарний код. Після цього все робиться спочатку. Для кожного циклу для виходів Q1..Q4 на виходах Q5..Q8 також генерується унітарний код. Тобто перша ступінь як би поділяється ще на дві ступіні: на першій (4 молодших розряда) унітарний код генерується за 1 такт, а на другій (4 старших розряда) – за 4 такти. На виходах дешифратора унітарний код має 16 розрядів (по кількості входів - 24 ) і формується за 1 такт. Як бачимо, дешифратор має інверсні виходи.

За часовими діаграмами побудуємо таблицю станів (табл.. 1.1.)

Табл..1.1.

|

№ такту |

D4 |

D3 |

D2 |

D1 |

Вихід “0” |

|

1 |

0 |

0 |

0 |

0 |

Q1 |

|

2 |

0 |

0 |

0 |

1 |

Q2 |

|

3 |

0 |

0 |

1 |

0 |

Q3 |

|

4 |

0 |

0 |

1 |

1 |

Q4 |

|

5 |

0 |

1 |

0 |

0 |

Q5 |

|

6 |

0 |

1 |

0 |

1 |

Q6 |

|

7 |

0 |

1 |

1 |

0 |

Q7 |

|

8 |

0 |

1 |

1 |

1 |

Q8 |

|

9 |

1 |

0 |

0 |

0 |

Q9 |

|

10 |

1 |

0 |

0 |

1 |

Q10 |

|

11 |

1 |

0 |

1 |

0 |

Q11 |

|

12 |

1 |

0 |

1 |

1 |

Q12 |

|

13 |

1 |

1 |

0 |

0 |

Q13 |

|

14 |

1 |

1 |

0 |

1 |

Q14 |

|

Продовження табл. 1.1. |

|||||

|

№ такту |

D4 |

D3 |

D2 |

D1 |

Вихід “0” |

|

15 |

1 |

1 |

1 |

0 |

Q15 |

|

16 |

1 |

1 |

1 |

1 |

Q16 |

У таблиці станів останній стовпчик показує, на якому з виходів при даній комбінації сигнал знаходиться на рівні логічного “0” (такий вихід лише один, бо код унітарний).

Висновок: ми дослідили роботу та внутрішню структуру прямокутного дешифратора з інверсними виходами.

Дослід 2. Дослід дешифратора у динамічному режимі роботи.

Ціль: Дослідити роботу дешифратора у динамічному режимі роботи.

Проведення досліду.

1. Зібрати дешифратор.

2. Під’єднати до входу D1 генератор імпульсів (A=4В, f=10KHz).

3. Зняти за допомогою логічного аналізатора часові діаграми з виходів.

4. Зніти за допомогою осцилографа часову діаграму з виходу Q1.

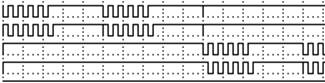

На рис. 2.1. показана схема проведення досліду.

Рис. 2.1. Схема проведення досліду 2

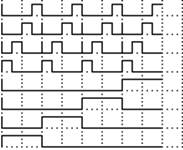

Тепер знімемо показники логічного аналізатора та осцилографа. Результати вимірів наведені на рис. 2.2. а), б)

![]()

Рис. 2.2. а). Показники логічного аналізатора.

Рис. 2.2. б). Показники осцилографа.

Як бачимо з часових діаграм, при частоті синхронізації меншій за частоту генератора імпульсів, за один такт синхронізації встигають пройти декілька сигналів з генератора імпульсів. Унітарність коду зберігається, з кожним сигналом з генератора імпульсів парність вхідного коду змінюється, отже змінюється й положення “0” у вихідному коді. У зв’язку з тим, що всі елементи ідеальні, на осцилограмі можна побачити передній фронт сигналу з генератора імпульсів при переході за синхросигналом на наступну “групу” кодів.

Висновок: ми дослідили роботу дешифратора у динамічному режимі роботи.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.