При построении схемы в программе Micro-Cap необходимо подключить к входам источники сигналов, формирующие тестовые последовательности. В этой работе в качестве таких источников удобно использовать генераторы тестовых сигналов, имеющие один выход (Component - Digital Primitives - Stimulus Generators - Stim1). После размещения такого генератора на схеме открывается окно задания атрибутов, в котором необходимо задать закон изменения во времени сигнала на его выходе, такой, чтобы получить составленную ранее для этого сигнала последовательность. Параметры генератора (текстовое поле .define в нижнем поле ввода) задаются в виде пар «время – логический уровень». Например, пусть необходимо получить такую последовательность, как показано на рисунке.

![]()

Каждое деление соответствует одной миллисекунде. В момент времени 0 мс сигнал принимает значение 0, затем в момент времени 9 мс — 1, и т.д. В итоге параметры генератора для формирования такой последовательности будут выглядеть следующим образом:

.define SEQ_D 0ms 0 9ms 1 13ms 0 16ms 1 17ms 0 20ms 1 28ms 0 30ms 1 34ms 0 38ms 1

SEQ_D — это имя вырабатываемой последовательности; должно быть различным для каждого генератора, присутствующего в схеме.

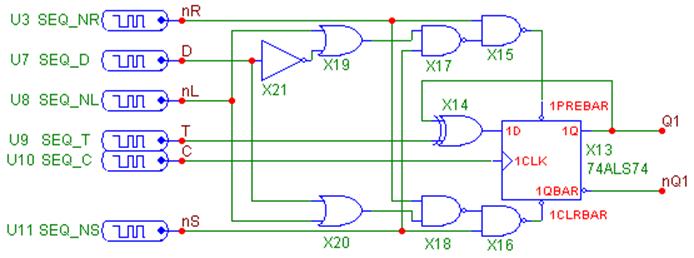

Важное замечание: неопределённое состояние триггера! При включении питания схемы состояние триггера не известно, с равной вероятностью триггер может установиться в 0 или в 1. Поэтому необходимо принудительно записать в триггер 0 или 1 в самом начале работы схемы, чтобы точно было известно исходное состояние и полученные как функция от него последующие состояния. Поскольку все используемые в данной работе триггеры имеют дополнительные асинхронные входы сброса и установки, сделать это достаточно просто. Допустим, начальное состояние триггера должно быть 1. Если у всего полученного сложного триггера есть асинхронный вход установки (как, например, в схеме на следующем рисунке, это сигнал nS), то необходимо так составить тестовые последовательности, чтобы в нулевой момент времени сразу же подать на этот вход импульс активного уровня (в данном примере так и есть, что видно на временных диаграммах на рисунке в конце этого раздела). Если же полученный сложный триггер не имеет входа асинхронной установки, то нужно подать импульс, устанавливающий триггер в 1, непосредственно на вход асинхронной установки интегрального триггера. Для этого к этому входу подключите генератор логических сигналов (Stim1), настроенный так, чтобы в нулевой момент времени выдать короткий импульс (вполне достаточно 10 мкс) активного уровня.

Ниже на рисунке приведён пример схемы, собранной на данном этапе. В этом примере используется D‑триггер микросхемы 74ALS74 и логические элементы ТТЛ. Сигналам присвоены имена, отражающие их назначение (входные сигналы — nR, nS, D, nL, T, C, выходные сигналы — Q1 и nQ1).

После того, как схема полностью собрана, необходимо построить временные диаграммы её работы, т.е. графики изменения во времени всех входных и выходных сигналов. Временные диаграммы строятся в режиме анализа переходных процессов (Transient Analysis). Параметры режима Transient Analysis необходимо задать так, чтобы составленные тестовые последовательности были полностью просчитаны и показаны на экране. То есть, в полях ввода X Range для каждого графика, а также в Time Range задаётся время, несколько большее, чем время самого последнего изменения входных сигналов.

Естественно, что временные диаграммы, построенные программой, должны полностью совпадать с построенными ранее вручную.

После того, как собрана и проверена схема с использованием типового интегрального триггера и построены временные диаграммы её работы, необходимо раскрыть внутреннюю структуру применённого триггера до уровня логических элементов. D‑триггер построить по схеме Master-Slave; JK‑триггер построить на основе D‑триггера, выполненного по схеме Master-Slave.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.