Изучение схем типовых триггеров и способов их построения из логических элементов.

Изучение методики синтеза триггера с заданным законом функционирования на основе типового триггера и анализ режимов его работы.

В каждом варианте задания задан некоторый триггер со сложным законом управления. Приведено его условное обозначение и описание режимов работы. Также указан тип логики (ТТЛ или КМОП), на микросхемах этого типа нужно реализовать схему. Требуется реализовать этот нестандартный триггер на основе стандартного синхронного D‑триггера или JK‑триггера с асинхронными входами установки и сброса, выпускаемого в сериях микросхем ТТЛ или КМОП.

1. Продумать тестовые последовательности, подаваемые на входы заданного триггера. Тестовые последовательности должны по возможности отражать все режимы работы триггера; в то же время нужно избегать запрещённых комбинаций входных сигналов. Построить временные диаграммы работы триггера (на бумаге): входные сигналы и сигналы на прямом и инверсном выходах.

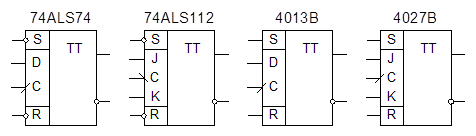

2. Представить заданный триггер в виде [схема управления + синхронный D-триггер], либо [схема управления + JK-триггер], в зависимости от варианта задания. В качестве синхронного D‑триггера ТТЛ используйте микросхему 74ALS74; КМОП — микросхему 4013B. В качестве JK‑триггера ТТЛ используйте микросхему 74ALS112; КМОП — микросхему 4027B. Условные обозначения этих триггеров показаны на следующем рисунке (каждая из этих микросхем содержит два одинаковых триггера; на рисунке показан только один из них).

3. Составить таблицу истинности для функций возбуждения триггера, вырабатываемых схемой управления.

4. Занести значения функций в карту Карно.

5. На основании карты Карно записать логические выражения для функций; преобразовать (упростить) их, ориентируясь на конкретные логические элементы из серий ИМС ТТЛ или КМОП в соответствии с вариантом задания.

6. Построить логическую схему, вырабатывающую функции возбуждения триггера и подключить к ней триггер.

7. Собрать полученную схему в программе Micro-Cap. Подключить к входам генераторы тестовых сигналов и задать параметры генерируемых сигналов так, чтобы получить составленные ранее тестовые последовательности. В режиме Transient Analysis построить временные диаграммы работы схемы. Убедиться, что они соответствуют заданному в задании закону функционирования триггера и полностью совпадают с построенными ранее на бумаге.

8. Раскрыть внутреннюю структуру используемого в задании типового триггера с асинхронными входами установки и сброса (D‑триггера или JK‑триггера, соответственно) до уровня логических элементов, ориентируясь на конкретные логические элементы из серий ИМС ТТЛ или КМОП в соответствии с вариантом задания. D‑триггер построить по схеме Master-Slave; JK‑триггер построить на основе D‑триггера, выполненного по схеме Master-Slave.

9. Собрать эту схему триггера в программе Micro-Cap. Подключить его входы параллельно одноимённым входам уже имеющегося в схеме интегрального триггера и построить временные диаграммы сигналов на прямом и инверсном выходах. Убедиться, что они совпадают с сигналами на прямом и инверсном выходах интегрального триггера.

Тестовые последовательности — это сигналы, подаваемые на входы триггера. Триггер в соответствии со своим законом функционирования реагирует на эти сигналы и выставляет определённые логические уровни на прямом и инверсном выходах. Как уже было сказано, нужно составить такие тестовые последовательности, чтобы наиболее полно отразить возможные режимы работы триггера. Примером тестовых последовательностей может служить приведённый в конце этого раздела рисунок, на котором изображены построенные программой Micro-Cap графики; первые шесть графиков — это входные сигналы. Но для того, чтобы получить информативные графики средствами программы, сначала нужно продумать, как будут изменяться входные сигналы (это удобно сделать на бумаге в клетку, привязывая фронты и спады к линиям разметки и считая одну клетку равной 1 мс). После составления тестовых последовательностей для входных сигналов начертите графики для выходных сигналов, т.е. сигналов на прямом и инверсном выходах триггера при заданных изменениях входных сигналов, руководствуясь заданным законом функционирования триггера.

Представление нестандартного триггера в виде сочетания схемы управления и типового триггера и синтез схемы управления были рассмотрены в курсе лекций, поэтому отметим лишь основные моменты. На схему управления заводятся все входные сигналы (кроме синхросигнала C) и сигнал с прямого выхода триггера. Выходные сигналы схемы управления подаются на входы типового триггера. Соответственно, для D‑триггера с асинхронными входами установки и сброса, это сигналы D, S, R, а для JK‑триггера с асинхронными входами установки и сброса — сигналы J, K, S, R.

При составлении таблицы истинности нужно обращать внимание на полярность входных сигналов триггеров. Так, например, триггеры микросхемы 74ALS74 имеют инверсные асинхронные входы сброса и установки, а 4027B — прямые. При запрещённых комбинациях входных сигналов следует считать выходные сигналы схемы управления неопределёнными, что в таблице истинности обозначается звёздочкой.

Схема управления строится на ИМС, выполненных по той же технологии (ТТЛ или КМОП), что и используемая в задании микросхема триггера. При составлении схемы и выборе логических элементов можно пользоваться таблицей, приведённой в приложении к первой работе, в которой перечислены логические элементы в сериях ИМС ТТЛ и КМОП.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.