11 :: 12;

12 :: 13;

13 :: 14;

14 :: 15;

15 :: 0;

16 :: 1;

17 :: 2;

18 :: 3;

19 :: 4;

20 :: 5;

21 :: 6;

22 :: 7;

23 :: 8;

24 :: 9;

25 :: 0;

ELSE :: 0;

END TRUTH_TABLE;

END PROM_DSL;

------------------------------------------------------------------------------------------------------------------------------------

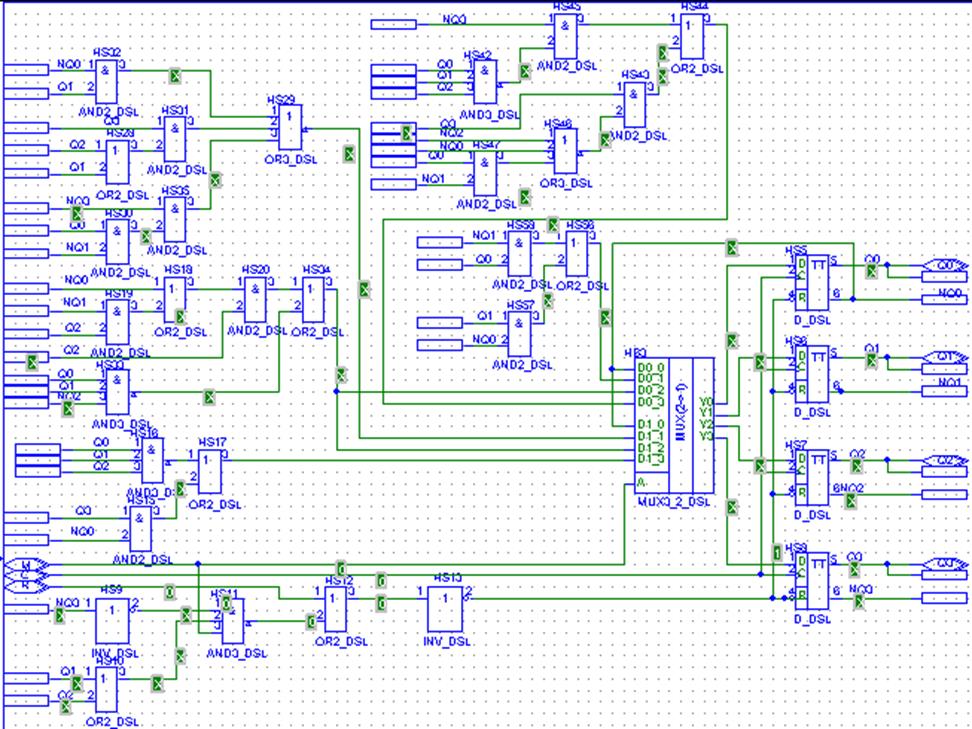

7. Синтез комбинационной части автомата на мультиплексоре, реализованном в виде иерархического DSL-символа.

Для реализации схемы используется трехразрядный мультиплексор 2 в 1. Частичные функции для его входов определяются по картам Карно.

В этой схеме так же добавлена логика для сброса счетчика.

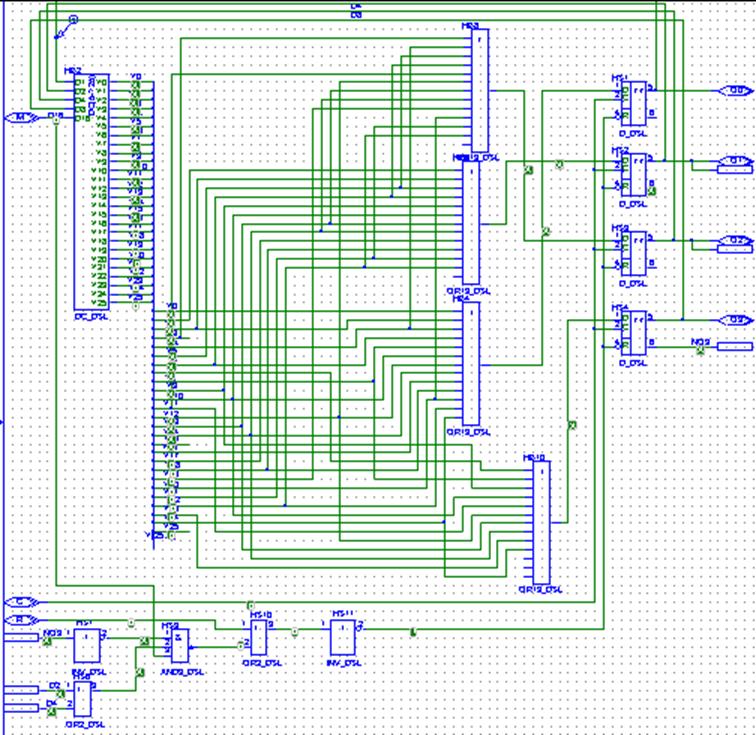

8. Синтез комбинационной части автомата на дешифраторе, реализованном в виде иерархического DSL-символа.

Схема реализуется на дешифраторе (5 в 26) на основании логической таблицы проектируемого автомата по СДНФ (без минимизации) каждой функции возбуждения. Схема замещения имеет вид:

В этой схеме так же добавлена логика для сброса счетчика

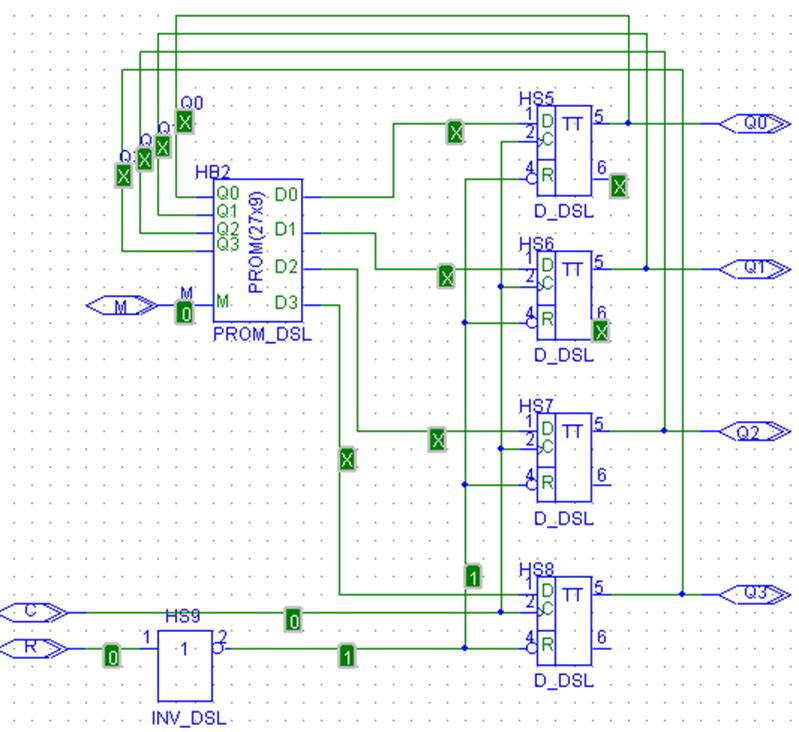

9. Синтез комбинационной части автомата на ПЗУ реализованного в виде иерархического DSL-символа. Все функции возбуждения "зашиты" в одно ПЗУ.

Использовано ПЗУ с организацией 27x9 бит. Его содержимое – все та логическая таблица данного автомата.

10. Выводы, личные впечатления.

На данную работу было затрачено значительное количество времени (примерно 20-30 часов). Были закреплены навыки работы с САПР DesignLab8, полученные еще при выполнении лабораторных работ, навыки работы с логическими таблицами и картами Карно. А так же приобретены новые знания, связанные с САПР DesignLab8 (например реализация счетчика на мультиплексорах, дешифраторах и ПЗУ).

Вообще понравилась работа с пакетом DesignLab8 (особенно в сравнении с MultiSim и ElectronicWorkBench), этот пакет очень удобен и относительно прост для понимания. В тоже время содержит множество библиотек с зарубежными элементами и множество полезных функций, которых не было в изученных ранее пакетах (например иерархические блоки, DSL, многолистовые схемы и мн.др.). Наверное единственное негативное впечатление, связанное с изученным пакетом – это множество файлов, используемых при проектировании (в РГР используется – 110 файлов), которые при этом имеют довольно сложную взаимосвязанность (и поэтому сложно переносятся на другой ПК). Из за этого усложняется верификация проекта.

Вообще верификация была самым сложным. Я столкнулся со множеством неожиданных проблем. Самым интересным оказалось то, что у D-триггера (7474) переключение из 0 в 1 и из 1 в 0 выполняется с разными задержками.(1->0 =20нс, а 0->1 = 14 нс). Из-за этого когда при счете один (или несколько) разрядов переключается из 0->1, а другой (другие) из 1->0, то счетчик сбивается на 20-14=6 нс (из 0->1 разряды уже переключились, а из 1->0 еще нет). По прошествии же 6 нс все оставшиеся разряды(1->0) переключаются, и счетчик продолжает корректный счет «как ни в чем не бывало».Это никак мною не устранялось, но на понимание этого «явления» потребовалось много времени.

Еще хотелось бы отметить, что после выполнения РГР работать с пакетом DesignLab8 стало еще быстрее, и многие вещи делаются просто на «автомате».

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.