Благодаря картам Карно получаем следующие формулы:

Q0=/Q0;

Q1=/Q0*Q1+M*Q3*(Q1+Q2)+Q0*/Q1*(/M+/Q3);

Q2=Q2*(/Q0+/Q1*Q2)+Q0*Q1*/Q2;

Q3=Q3*(/Q0+/M*/Q2+/M*Q0*/Q1)+Q0*Q1*Q2*(M+/M*/Q3);

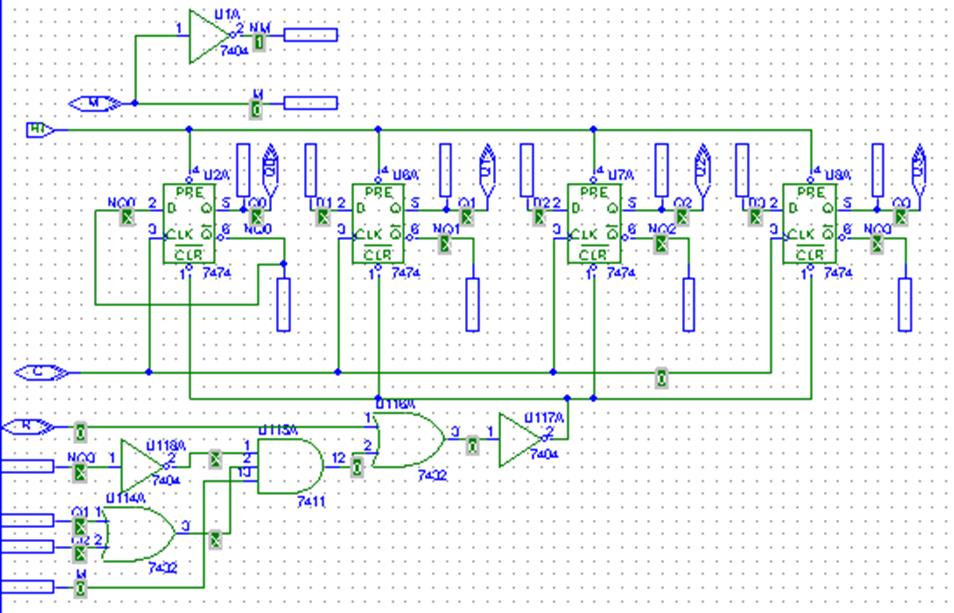

Далее по этим формулам строим двухлистовую схему:

Page 1:

Помимо логики, построенной по формулам, в эту страницу (Page 1) добавлена логика для сброса счетчика в том случае, если производится переход из MODE=0 в MODE=1, и при этом его значение >=A и <=F.

Т.е. для корректной работы двоично-десятичного счетчика необходимо сбрасывать счет, если предыдущее значение выходило за пределы его допустимых значений (а это возможно только при переключении из M=0 в M=1).

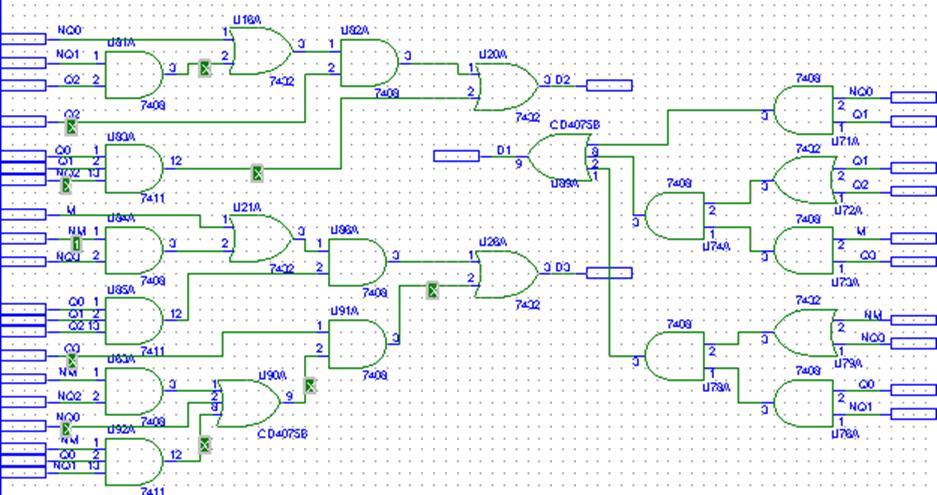

Page 2:

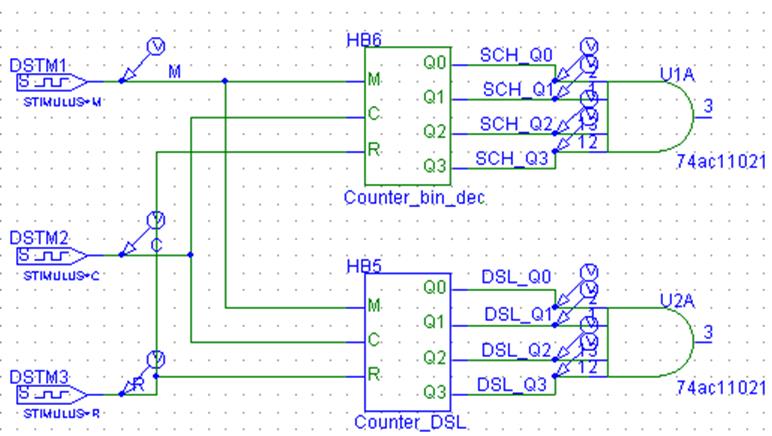

Эта схема является также и схемой замещения для цифрового автомата(ЦА) в виде иерархического блока. А верхний уровень иерархии для ЦА выглядит так:

В этой схеме так же находится иерархический блок с поведенческой DSL- моделью (следующий пункт).

Вообще все последующие схемы верхнего уровня одинаковы (за исключением самих иерархических блоков), поэтому далее проводится не будут.

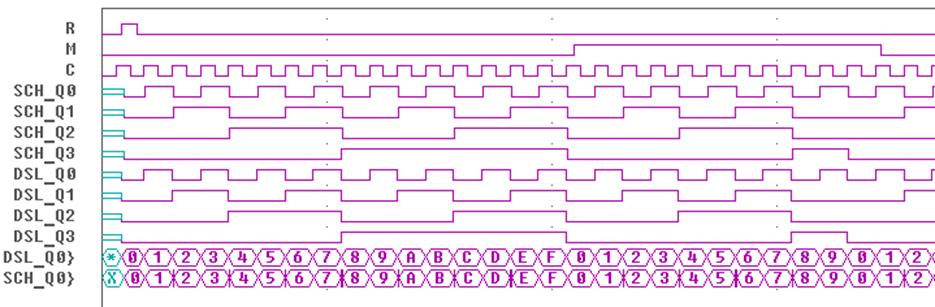

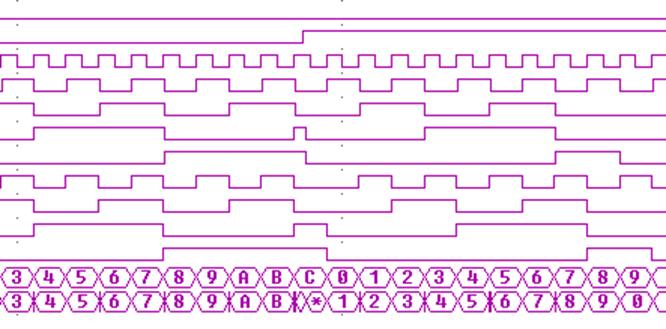

Верификация схемы:

Проведен довольно большой эксперимент, чтобы показать полный обход счетчика при M=0 и M=1, а так же переключение из М=0 в М=1 при Q[3]=C.

5. Проектирование поведенческой DSL-модели цифрового автомата.

Составлям DSL-модель:

PROCEDURE Counter_DSL (

INPUT M, C, R ;

OUTPUT Q0, Q1, Q2, Q3 CLOCKED_BY C RESET_BY R;

);

IF [(M*(Q1+Q2)*Q3)=1] THEN Q0=0; Q1=0; Q2=0; Q3=0;

ELSE

Q0=/Q0;

Q1=/Q0*Q1+M*Q3*(Q1+Q2)+Q0*/Q1*(/M+/Q3);

Q2=Q2*(/Q0+/Q1*Q2)+Q0*Q1*/Q2;

Q3=Q3*(/Q0+/M*/Q2+/M*Q0*/Q1)+Q0*Q1*Q2*(M+/M*/Q3);

END IF;

END Counter_DSL;

6. Разработка иерархических символов, поддерживаемых DSL-моделями и используемых в проекте.

В работе используются следующие элементы: НЕ, И2, ИЛИ2, И3, ИЛИ3, ИЛИ13, трехразрядный мультиплексор 2 в 1, D-триггеры, дешифратор 5 в 26, ПЗУ с организацией (27х9).

Их внешний вид можно посмотреть в последующих пунктах задания, а DSL- модели приведены ниже:

------------------------------------------------------------------------------------------------------------------------------------

PROCEDURE INV_DSL (INPUT Q; OUTPUT Y);

Y=/Q;

END INV_DSL;

------------------------------------------------------------------------------------------------------------------------------------

PROCEDURE AND2_DSL (INPUT Q0, Q1; OUTPUT Y);

Y=Q0*Q1;

END AND2_DSL;

------------------------------------------------------------------------------------------------------------------------------------

PROCEDURE AND3_DSL (INPUT Q0, Q1, Q2; OUTPUT Y);

Y=Q0*Q1*Q2;

END AND3_DSL;

------------------------------------------------------------------------------------------------------------------------------------

PROCEDURE OR2_DSL (INPUT Q0, Q1; OUTPUT Y);

Y=Q0+Q1;

END OR2_DSL;

------------------------------------------------------------------------------------------------------------------------------------

PROCEDURE OR3_DSL (INPUT Q0, Q1, Q2; OUTPUT Y);

Y=Q0+Q1+Q2;

END OR3_DSL;

------------------------------------------------------------------------------------------------------------------------------------

PROCEDURE OR13_DSL (

INPUT P1, P2, P3, P4, P5, P6, P7, P8, P9, P10, P11, P12, P13 ;

OUTPUT Y ;

);

Y=P1+P2+P3+P4+P5+P6+P7+P8+P9+P10+P11+P12+P13;

END OR13_DSL;

------------------------------------------------------------------------------------------------------------------------------------

PROCEDURE MUX2_3_DSL (

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.