Предусмотренный в задании контроль паритета SRAM опущен т.к разработчик данной микросхемы даёт гарантию 100% на доброкачественную работу своих схем, кроме того чисто практически контроль паритета в настоящее время плохо используется, ведь он способен только обнаруживать ошибки нечетной кратности, а если 2 бита повреждены - схема не обнаружит ошибки; кроме того существует достаточно большая вероятность того, что ошибка будет в самом контрольном бите. Предположим схема контроля паритета обнаружила ошибку, происходит обращение к системе обработки прерываний, и....все , исправить ее мы не можем.

Все микрооперации с основной памятью отличаются положительным значением бита микрокоманды (МЕМ). Запись/чтение основной памяти управляется ,битом микрокоманды (WE#).

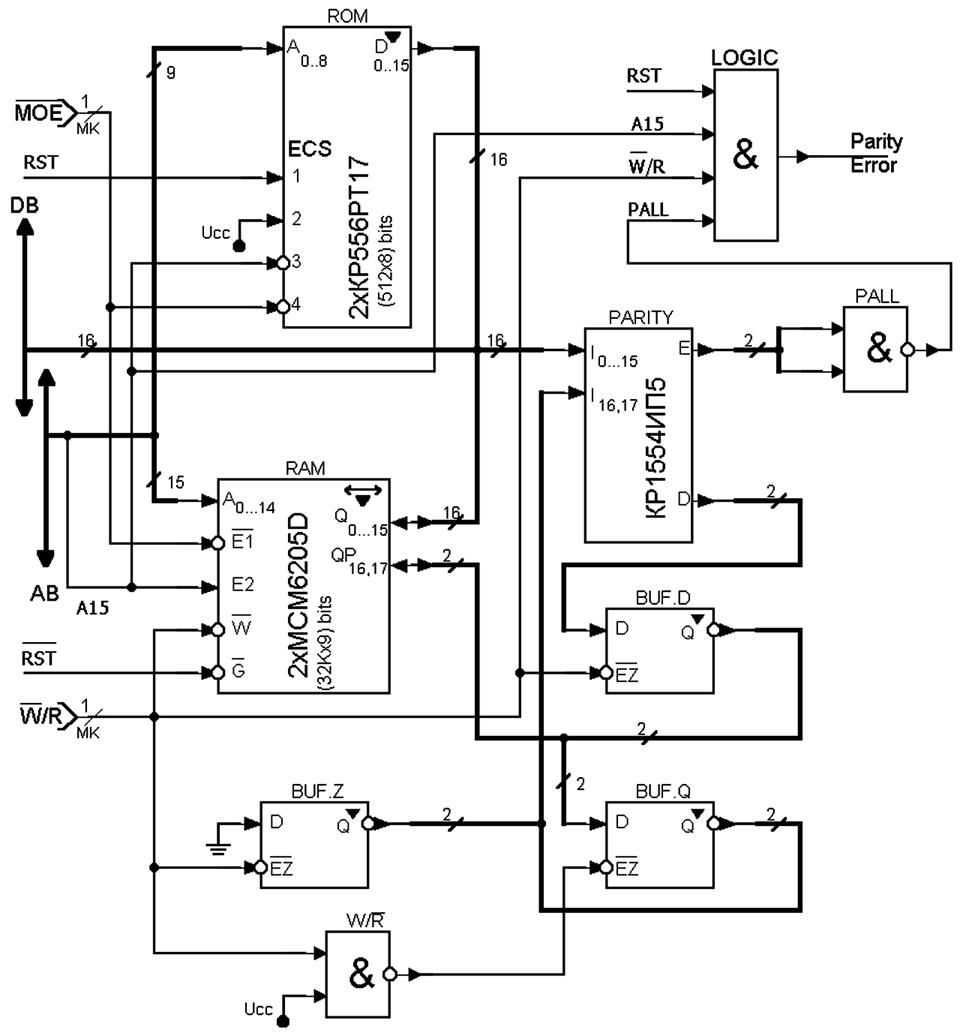

Предусмотренный в задании контроль паритета SRAM мог бы быть опущен т.к разработчик данной микросхемы даёт гарантию 100% на доброкачественную работу своих схем, но так как главная цель КР –учебная, то для укрепления навыков проектирования простых логических схем контроль паритета решено разрабатывать, и он разрабатывается следующим образом . При записи в ОЗУ данные идущие на входы побайтово свёртываются по модулю 2, и записываются в специально отведённую для этого микросхему,CY7C123-15 с организацией 256Кx4 бит ,по тому же адресу, что и в основной памяти. При чтении данные и паритетные биты поступают на высокоскоростную схему контроля чётности К1500ИП160 (tзр=3нс), источник [2], где формируется четыре бита ошибки паритета – по одному на каждый байт ,затем с помощью схемы ИЛИ ,К531ЛЛ1 с временем задержки распространения 7нс источник [3], формируется окончательный бит ошибки паритета.

Структурная схема ОП и временные диаграммы работы ОП в приложении 2.

Выводы.

В результате выполнения данной работы мною было разработанно ядро микроЭВМ с использованием заданной элементной базы. МикроЭВМ, построенное на основе этого ядра, работало бы с максимальной частотой в 10 МГц.

Цели данной работы подробно сформулированны в [1]. Считаю, что они достигнуты, хотя это моя первая работа такого масштаба и предмета для сравнения у меня нет. Поэтому одним из полезных последствий выполнения этой работы для меня явилось приобретение опыта выполнения подобных работ.

В процессе решения поставленной задачи закрепились на практике теоретические знания, полученные на курсе схемотехники, понимание взаимодействий между различными элементами схемы стало глубже. В целом работа оказала большую помощь в приобретении практических знаний по разработке устройств ЭВМ.

Схема контроля паритета (КР1554ИП5) [2, c.387]. Получает 9-ти разрядное слово и выдаёт “1” на выходе E в случае чётности числа единиц во входном слове и “1” на D в ином случае. Работа схемы очень проста и удобство её применения именно в этом. При чтении бит чётности берётся из памяти, при записи – всегда 1.

PALL (КР1533ЛА3) [2]. Служит для «объединения» сигналов ошибки паритета. Если хоть в одном байте возникла ошибка, то на выходе этого элемента будет «1».

LOGIC (КР1533ЛИ6) [2]. Реализует функцию «И» над четырьмя сигналами. Выдаёт логическую единицу только в том случае, если в текущем цикле выбран кристалл оперативной памяти (A15=1), производится чтение (#W/R=1), имеется действительная ошибка паритета (PALL=1) и нет активного сигнала сброса (RST=1). Более коротко об этом можно сказать так – генерация запроса на прерывание по ошибке паритета. Дальнейший путь сигнала ошибки паритета я не рассматривал, т.к. это относится к организации прерываний в ЭВМ, а данный вопрос при постановке задачи на курсовую работу не ставился.

Для обеспечения обмена данными между памятью и шиной данных необходим интерфейсный элемент, так как он рассчитан на большую нагрузочною способность, в качестве такового полагается целесообразным использование буферных элементов, по причине наличия возможности обеспечения целенаправленного обмена. Кроме того, использование регистров, обеспечило бы конвейерную структуру, а необходимость конвейера отсутствует.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.