2.3 Определение необходимого количества МС для построения накопителя:

- количество

микросхем

- количество

микросхем

- количество физических страниц

- количество физических страниц

Таким образом, для построения нашего модуля требуется 4-ре микросхемы CY7C018-20 64К×9, из которых получится одна физическая страница. Значит, нам не потребуется дешифратор активации физической страницы.

Посчитаем разрядность шины адреса:

64К = 43×210=26×210=216, т.о. разрядность шины адреса равна 16-ти.

2.4 Организация накопителя:

Изобразим карту памяти:

|

FFFFFFFF Н Е И С П О Л Ь З У Е Т С Я 80010000 |

|

8000FFFF Н Е И С П О Л Ь З У Е Т С Я 80000000 |

|

7FFFFFFF Н Е И С П О Л Ь З У Е Т С Я 20000 |

|

1FFFF SRAM 0 |

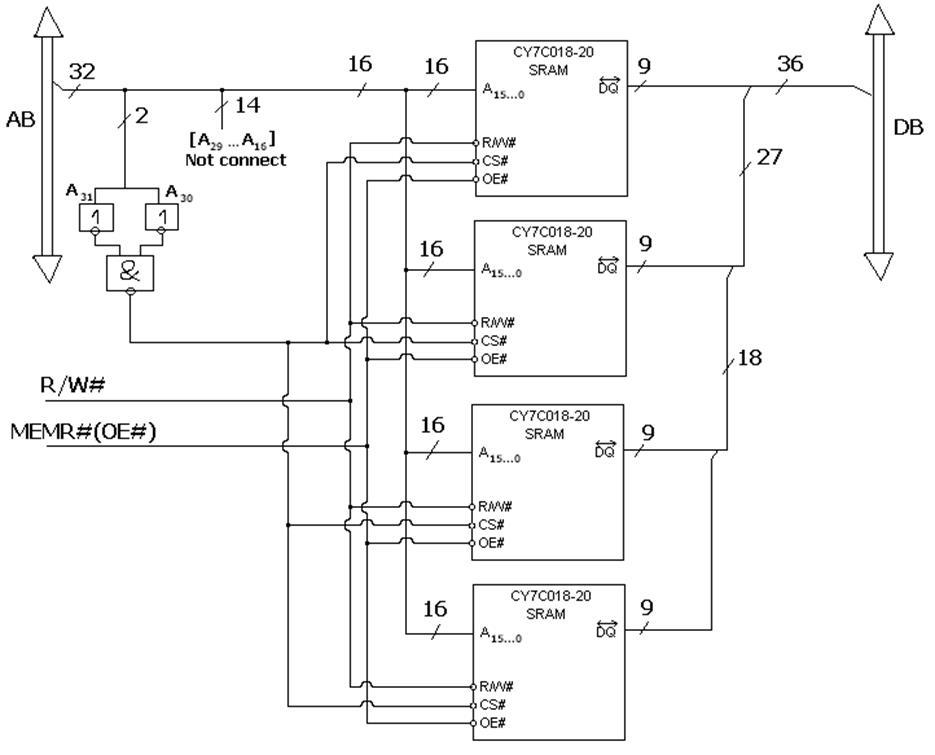

Расположение памяти в нижних адресах карты памяти обеспечивается использованием двух старших битов адреса. Конъюктивно объединяя эти биты, подаем на входы CS# для управления работой всех МС по входам выбора кристалла, так как в нашем случае необходимо обеспечить ввод (вывод) данных сразу во все микросхемы (из всех микросхем). Выше сказанное отражено на электрической схеме (рис.5).

Рис. 4 Карта памяти

Изобразимэлектрическую схему (без обвязки):

Рис.5 Электрическая схема накопителя без обвязки.

2.5 Выбор интерфейсных элементов (буферов):

Чтобы исключить конфликты при доступе к системным шинам адреса и данных, необходимы интерфейсные элементы (буферы). Они должны включаться в разрыв между шинами AB и DB. На шине данных DB буферы снижают нагрузку на выходах ИМС памяти и предотвращают конфликты, причем необходимо включить двунаправленные буферы с возможностью перехода в Z-состояние, т.к. данные могут передаваться как на запись, так и на чтение. На шине адреса AB буферы также снижают нагрузку, переход в Z-состояние и двунаправленная передача не нужны. На шине управления мы применяем вентили, которые стабилизируют емкостную нагрузку (в соответствии со стандартом ТТЛ).

2.5.1 Определение коэффициентов объединения:

При выборе буферов в схемной обвязке определяют коэффициенты объединения по всем функциональным входам накопителя:

![]() - по

входам адресов

- по

входам адресов

- по входам (выходам) данных

- по входам (выходам) данных

- по входам разрешения чтения

(записи)

- по входам разрешения чтения

(записи)

2.5.2 Определение нагрузки создаваемой накопителем, без схем согласования:

Нам необходимо определить нагрузку, создаваемую функциональными входами накопителя на функциональные шины (линии) системной магистрали в отсутствии схем согласования (буферов).

![]()

Емкость монтажа: ![]() .

Допустим, емкость монтажа равна 10(пФ).

.

Допустим, емкость монтажа равна 10(пФ).

![]() - из документации по МС.

- из документации по МС.

Тогда: ![]() .

.

В случае использования микросхемы по ТТЛ(Ш) технологии рассчитываются также значения входных токов накопителя на высоком и низком уровне сигналов, но в нашем случае, при использовании микросхем КМОП (CMOS) технологии, требуется учитывать только параметры емкостной нагрузки.

Пиковое значение емкостной нагрузки не должно превышать 10(пФ) (по стандарту ТТЛ). Наши полученные значения превышают данную величину, а согласно требованиям технического задания, интерфейс микросхемы модуля асинхронной памяти должен соответствовать ТТЛ – интерфейсу. Значит, нам необходимо скорректировать емкостную нагрузку, вводя соответствующие схемы согласования (буферы). Критерий, по которому мы будем их выбирать - это сравнение параметра, заданного в интерфейсе, с параметром, который рассчитан нами, исходя из действительных данных.

2.5.3 Выбор типономинала схемы согласования:

![]() Для буферизации шины адреса были выбраны 16

- разрядные однонаправленные буферы FCT16244T фирмы IDT (FAST CMOS 16-BIT BUFFER DRIVER). А для буферизации шины

данных были выбраны 18 – разрядные двунаправленные буферы FCT162701T той же фирмы (FAST

CMOS 18-BIT READ/WRITE BUFFER). Выходной буфер данных

способен управлять направлением пересылки данных (управляющий вход LE). При операции чтения буфер работает на выход, т.е. данные

поступают на шину данных (LE = H),

при записи - на вход (данные поступают с шины данных; (LEv

Для буферизации шины адреса были выбраны 16

- разрядные однонаправленные буферы FCT16244T фирмы IDT (FAST CMOS 16-BIT BUFFER DRIVER). А для буферизации шины

данных были выбраны 18 – разрядные двунаправленные буферы FCT162701T той же фирмы (FAST

CMOS 18-BIT READ/WRITE BUFFER). Выходной буфер данных

способен управлять направлением пересылки данных (управляющий вход LE). При операции чтения буфер работает на выход, т.е. данные

поступают на шину данных (LE = H),

при записи - на вход (данные поступают с шины данных; (LEv = L).

= L).

.

Для буферизации шины адреса и шины данных ПЗУ был выбран восьмиразрядный буфер КР1554АП5, а для шины данных ОЗУ - восьмиразрядный двунаправленный буфер КР1554АП6, который обеспечивает как возможность чтения, так и записи. Микросхема КМ1804ГГ1 была выбрана в качестве задающего генератора, потому что она позволяет формировать множество выходных сигналов различной формы, достаточно гибко управлять длительностью цикла, а также эта микросхема обладает широким диапазоном выдаваемых частот.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.