Как видно из таблицы, преобразованный модуль (с учетом заземленных #BLE и #BHE) теперь реализует 4 состояния: модуль отключен, чтение слова, запись слова, модуль выбран выводы отключены.Ниже на рис.2 представлена функциональная схема модуля памяти.

|

Рис.2 Функциональная схема модуля памяти (128*32)бит |

Таблица 3 Приложение к схеме накопителя (рис.2)

|

Обозначение |

Наименование |

Назначение |

|

DD1…4 |

Модуль SRAMсерии 7C1021B-15 |

Накопитель информации |

|

ADDRSEL |

Адресный селектор |

Проверка оперативной ли памяти предназначен адрес, формирование управляющих сигналов |

|

TR1 |

Трансивер, серия CY74FCT16245T. |

Прием и передача старших 16 битов данных |

|

TR2 |

Трансивер, серия CY74FCT16245T |

Прием и передача младших 16 битов данных |

|

BF1 |

Буфер, серия CY74FCT16244T |

Передача 16 младших битов адреса. |

|

BF2 |

Буфер, серия CY74FCT16244T |

Передача 2 старших битов адреса |

Для снижения нагрузки на выходы ИМС памяти и предотвращения конфликтов на DB применены буферы. Причём на шину DB необходимо включить двунаправленные буферы.

Описание выводов и функционально значимых линий функциональной схемы модуля памяти (рис.2)

A – внутренняя шина адреса

АВ – магистральная шина адреса

DQ – двунаправленная внутренняя шина данных

DВ – магистральная шина данных

CB – шина управления, состав:

MEMR – сигнал активации памяти, высокий уровень разрешает работу памяти, низкий соответствует её пассивному состоянию.

DD1

DQ0…15 - младшие разряды 32-х разрядного слова

А0…16 - шина адреса

DD2

DQ16…31 - старшие разряды 32-х разрядного слова

A0..16 – шина адреса

DD3

DQ0…15 - младшие разряды 32-х разрядного слова

А0…16- шина адреса

DD4

DQ16…31 - старшие разряды 32-х разрядного слова

A0.16– шина адреса

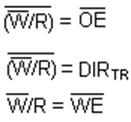

#W/R – сигнал выбора запись/чтение

#CE – вход выбора кристалла

#WE – вход разрешения записи

#OE – вход разрешения вывода

#BHE – вход разрешения записи/чтения старшего байта

#BLE – вход разрешения записи/чтения младшего байта

GND – заземление

Выходы адресного селектора:

1 – сигнал #CE для DD1, DD2

2 – сигнал #WE для DD1, DD2, DD3, DD4

3 – сигнал #CE для DD3, DD4

4 – сигнал #OE для DD1, DD2, DD3, DD4

5 – сигнал #OE - разрешение вывода для буферов

6 – сигнал DIR - управление направлением передачи данных трансивером

Некоторые особенности работы схемы:

Помимо адресов на входы селектора подаются управляющие сигналы, из которых формируются сигналы #OE трансивера и DIR трансивера. DIR зависит от уровня сигнала #W/R, #ОЕ устанавливается низким уровнем, если обращение идет к нашей памяти. Если сигнал MEMR на низком уровне, то память находится в пассивном состоянии, отключается трансивер. Модуль памяти не должен быть все время подключен к внешней магистрали. Отключение от внешних магистралей происходит следующим образом: если обращение не к разработанному модулю, то микросхемы памяти переводятся в пассивное состояние сигналом CE, а трансивер переводит шины в состояние высокого импеданса. Таким образом, разработанный модуль не добавляет нагрузку на общую линию и не мешает обмену данными между устройствами. Управление буфером не осуществляется, но создаваемая им нагрузка (т.к. он все время открыт для пропуска адреса) не мешает работе других устройств.

Адресный селектор построен на программируемой логике серии ATF1502ASL.

Его основные характеристики:

· Число входов – 16

· Число выходов – 16

· Напряжение питания – 5В±5%

· Время задержки распространения сигнала - 7.5нс.

Принцип работы адресного селектора:

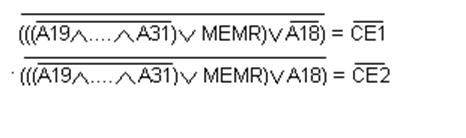

Сигналы управления формируются по следующим законам:

Сигналы управления формируются по следующим законам:

![]()

#CE1-активизация первой физической страницы низким уровнем сигнала.

#CE2-активизация второй физической страницы низким уровнем сигнала.

Адресный селектор реализует переключение выбора физических страниц согласно вышеописанным законам. При этом активной может быть только одна физическая страница. Сигнал активации/пассивизации выходных интерфейсных элементов формируется инвертированием сигнала MEMR. К недостаткам адресного селектора можно отнести то, что сигнал #WE и #OE формируется один для всех модулей памяти. Тем не менее, конфликтов это не вызывает, т.к. обращение к памяти за один такт возможно только к одной странице, а вторая блокируется высоким уровнем #CE, а вход выбора кристалла имеет более высокий приоритет по сравнению со входами разрешения записи/чтения. Кроме этого, к недостаткам можно отнести то, что при низком уровне MEMR также возможна установка низкого уровня на #WE или #OE, но это также не влечет нежелательных последствий, т.к. сама память в этом случае блокирована высоким #CE, а интерфейсные элементы переводят свои шины в состояние высокого импеданса, что блокирует не запрошенный ввод/вывод.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.