МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

НОВОСИБИРСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

КАФЕДРА ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ

Расчётно-графическая работа

по дисциплине «Микропроцессорные системы»

Факультет: АВТФ Преподаватель:

Группа: АМ-710 Дружинин А.И.

Студент: Эйрих Н.

Вариант: 22

Новосибирск, 2011

1. Постановка задачи. 3

2. Разработка микропроцессорной системы.. 3

2.1 Разработка структурной схемы.. 3

2.2 Разработка принципиальной электрической схемы.. 14

3. Программирование периферийных БИС.. 17

4. Выводы.. 20

Список литературы.. 21

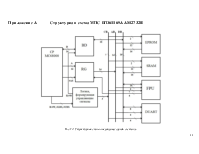

Приложение A............ Структурная схема МПС ITD6116SA AM2732B.. 22

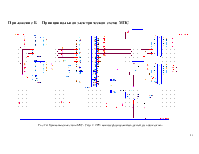

Приложение Б Принципиальная электрическая схема МПС.. 23

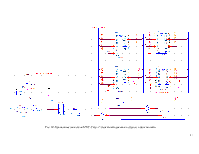

Приложение В Спецификация. 26

Разработать микропроцессорную систему на базе микропроцессора M68000, содержащую:

- 8 кБ ROM памяти;

- 4 кБ RAM памяти;

- периферийные БИС:

- MC68881 – арифметический сопроцессор (FPU);

- MC68681 – сдвоенный асинхронный приемопередатчик (DUART).

Разработка микропроцессорной системы по заданным требованиям предполагает выбор элементной базы, разработку структурной схемы с указанием основных связей и шин, разработку принципиальной электрической схемы микропроцессорной системы с синтезом недостающих блоков и соединением всех выводов микросхем, входящих в её состав.

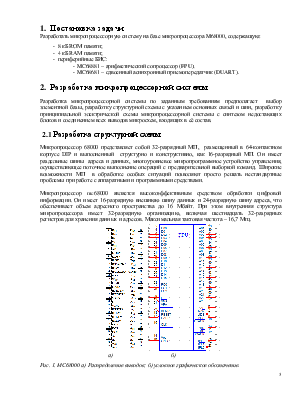

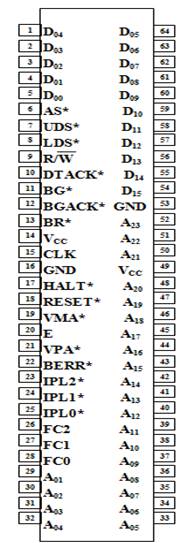

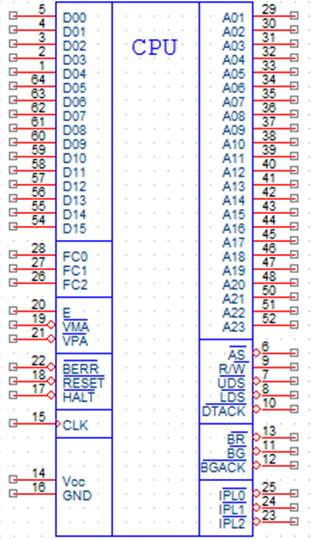

Микропроцессор 68000 представляет собой 32-рaзрядный МП, размещенный в 64-контaктном корпусе DIP и выполненный структурно и конструктивно, как 16-рaзрядный МП. Он имеет раздельные шины адреса и данных, многоуровневое микропрограммное устройство управления, осуществляющее поточное выполнение операций с предварительной выборкой команд. Широкие возможности МП в обработке особых ситуаций позволяют просто решать нестандартные проблемы при работе с аппаратными и программными средствaми.

Микропроцессор mc68000 является высокоэффективным средством обработки цифровой информации. Он имеет 16-разрядную внешнюю шину данных и 24-разрядную шину адреса, что обеспечивает объем адресного пространства до 16 Мбайт. При этом внутренняя структура микропроцессора имеет 32-разрядную организацию, включая шестнадцать 32-разрядных регистров для хранения данных и адресов. Максимальная тактовая частота – 16,7 Мгц.

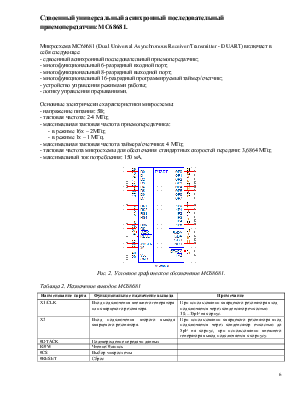

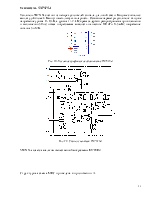

а) б)

Рис. 1. MC68000 а) Распределение выводов; б) условное графическое обозначение.

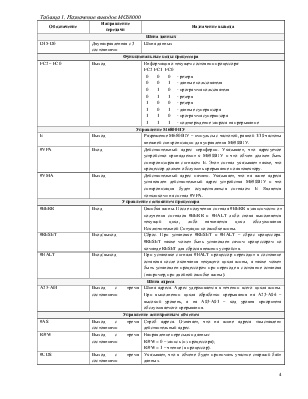

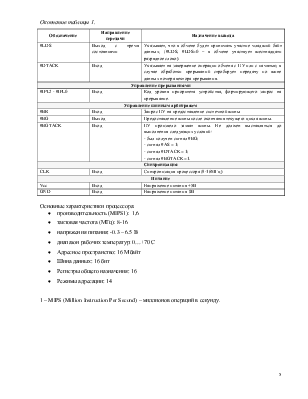

Таблица 1. Назначение выводов MC68000

|

Обозначение |

Направление передачи |

Назначение вывода |

|

Шина данных |

||

|

D15-D0 |

Двунаправленная с 3 состояниями |

Шина данных |

|

Функциональные коды процессора |

||

|

FC2 – FC0 |

Выход |

Информация о текущем состоянии процессора: FC2 FC1 FC0 0 0 0 - резерв 0 0 1 - данные пользователя 0 1 0 - программа пользователя 0 1 1 - резерв 1 0 0 - резерв 1 0 1 - данные супервизора 1 1 0 - программа супервизора 1 1 1 - подтверждение запроса на прерывание |

|

Управление M6800 ПУ |

||

|

E |

Выход |

Разрешение M6800ПУ – импульсы с частотой, равной 1/10 частоты внешней синхронизации для управления M6800ПУ. |

|

#VPA |

Вход |

Действительный адрес периферии. Указывает, что адресуемое устройство принадлежит к M6800ПУ и что обмен должен быть синхронизирован сигналом E. Этот сигнал указывает также, что процессор должен обслужить прерывание по автовектору. |

|

#VMA |

Выход |

Действительный адрес памяти. Указывает, что на шине адреса установлен действительный адрес устройства M6800ПУ и что синхронизация будет осуществляться сигналом Е. Является «откликом» на сигнал #VPA. |

|

Управление состоянием процессора |

||

|

#BERR |

Вход |

Ошибка шины. После получения сигнала #BERR в зависимости от получения сигналов #BERR и #HALT либо снова выполняется текущий цикл, либо начинается цикл обслуживания Исключительной Ситуации по ошибке шины. |

|

#RESET |

Вход/выход |

Сброс. При установке #RESET и #HALT – сброс процессора. #RESET также может быть установлен самим процессором по команде RESET для сброса внешних устройств. |

|

#HALT |

Вход/выход |

При установке сигнала #HALT процессор переходит в состояние останова после окончания текущего цикла шины, а также может быть установлен процессором при переходе в состояние останова (например, при двойной ошибке шины). |

|

Шина адреса |

||

|

A23-A01 |

Выход с тремя состояниями |

Шина адреса. Адрес удерживается в течении всего цикла шины. При выполнении цикла обработки прерывания на А23-А04 – высокий уровень, а на А03-А01 – код уровня приоритета обслуживаемого прерывания. |

|

Управление асинхронным обменом |

||

|

#AS |

Выход с тремя состояниями |

Строб адреса. Означает, что на шине адреса «выставлен» действительный адрес. |

|

R/#W |

Выход с тремя состояниями |

Направление пересылки данных: R/#W = 0 – запись (из процессора); R/#W = 1 – чтение (в процессор). |

|

#UDS |

Выход с тремя состояниями |

Указывает, что в обмене будет принимать участие старший байт данных. |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.