Тип 2 - При работе по этому типу канал А используется для двунаправленной передачи данных, канал С — для записи управляющих сигналов, обеспечивающих передачу данных по каналу А. Управляющие сигналы являются комбинацией сигналов, необходимых при работе канала А по типу 1.

Комбинации режимов задаются путем записи управляющего слова по адресу регистра управления схемы. В регистр управления можно только записывать управляющие слова. Чтение информации из регистра управления недопустимо.

Так как схема КР580ВВ55 не имеет внутреннего регистра, указывающего на состояние схемы, то для его определения считывают содержание регистра канала С и интерпретируют отдельные его разряды. При работе схемы по типу 1 или 2 можно изменять содержание отдельных разрядов канала С с помощью управляющего слова, записываемого в регистр управления.

К555ИР2 – регистр-защелка входного байта D0..D7. По команде #E0=1, выходные провода разорваны (Z). #E0=0 – выходы разрешены. При РЕ=1 слово D0..D7 можно отобразить на выходах. Когда РЕ=0, входное слово будет защелкнуто в регистр.

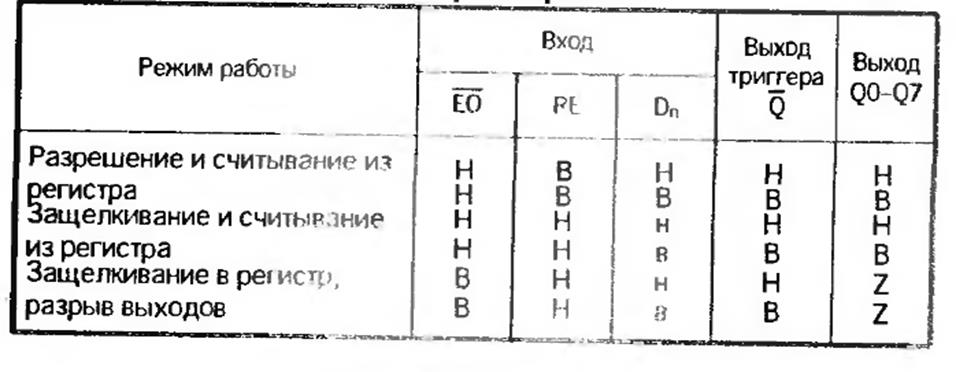

Состояние регистра К555ИР2 приведено в таблице 3.4.

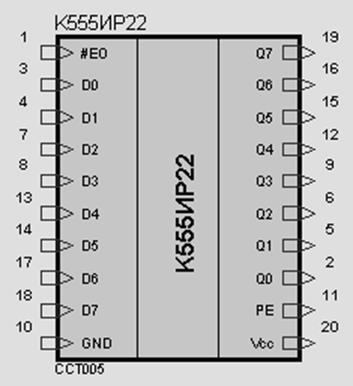

УГО К555ИР2 приведено на рисунке 3.9.

Таблица 3.4 – Состояние регистра К555ИР2

Рисунок 3.9 - УГО К555ИР22

K155ИД3 – преобразует полный двоичный четырехразрядный код в активный сигнал 1 на выходе с нужным десятичным номером. Два вывода #Е0 и #Е1 служат для запрета приема кодов (при #Е0 = 1 или #Е1 =1) или для разрешения дешифрации, когда #Е0 = #Е1 = 0. ИДЗ можно использовать как коммутатор-демультиплексор последовательных слов на любой из 16 выходов. Подаем на входы АЗ... А0 байт нужного нам адреса (1001 — это 9). Входы #Е0,#Е1 (или оба) принимают последовательные cлова, которые появятся без инверсии на выходе (у нас: 9). Ненужный вход Е заземляем. Если входной байт А0... АЗ генерируется асинхронным счетчиком, с помощью входов Е0,1 его можно синхронизировать, устранив "подмаргивание" выходных индикаторов в ответ на ложные входные коды.

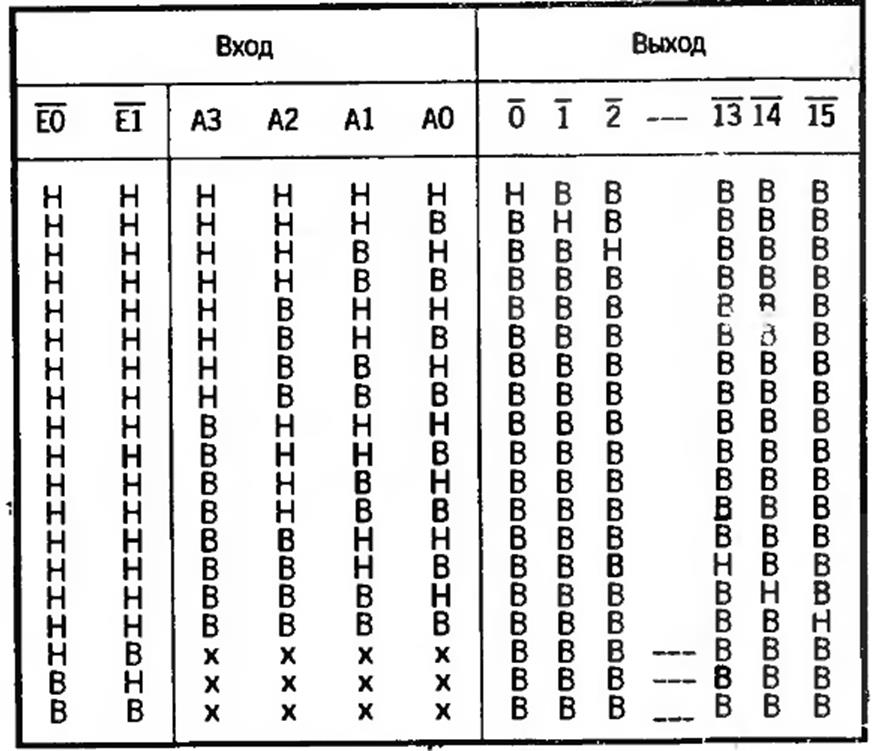

Состояние дешифратора K155ИД3 приведено в таблице 3.5.

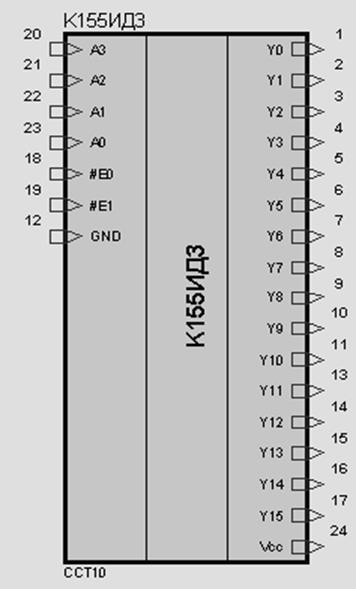

УГО K155ИД3 приведено на рисунке 3.10.

Таблица 3.5 – Состояние дешифратора K155ИД3

Рисунок 3.10 - УГО K155ИД3

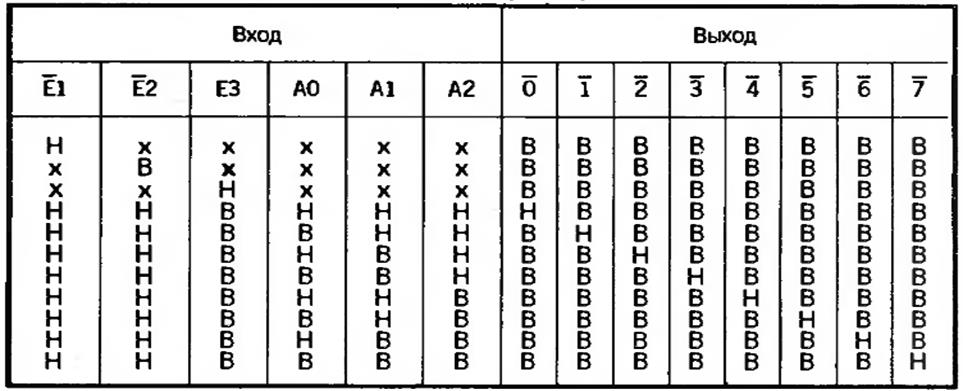

К155ИД7 — дешифратор 3-разрядного кода А0 ... А2 в уровень 1 на одном из 8 выходов: Y0... Y7. Входов разрешения - три. Дешифрация происходит при ЕЗ = 1, #Е1 = #Е2 = 0. Другое сочетание уровней дает 1 на всех выходах. Прибор работает как мультиплексор с 8 выходами: данные поступают на любой вход Е, на остальные — подаем уровень разрешения выхода, выбранного байтом адреса А0 ... А2. Неполный, на 24 выхода дешифратор 5-разрядного кода А0 ... А4 получается простым соединением одноименных входов трех микросхем. Вход АЗ — общий провод Е, А4 — #Е. Оставшийся вход #Е — разрешение. Добавив инвертор, получим от четырех ИД7 32 выхода.

Состояние дешифратора K155ИД7 приведено в таблице 3.6.

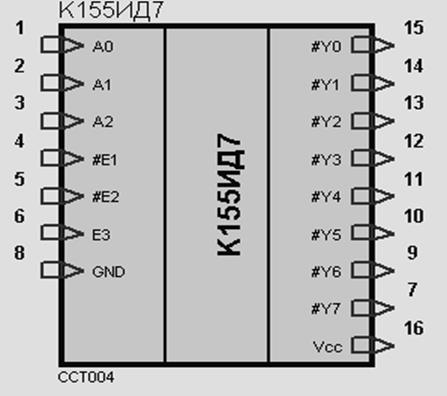

УГО K155ИД7 приведено на рисунке 3.11.

Таблица 3.6 – Состояние дешифратора K155ИД7

Рисунок 3.11 - УГО K155ИД7

Восьмиразрядные шинные формирователи применяются как буферные устройства шины данных в микропроцессорных системах. Большая выходная мощность и простота управления позволяет использовать их для построения двунаправленных согласующих буферов межмодульной связи либо как простые усилительные каскады.

Формирователь состоит из восьми одинаковых функциональных блоков с общими сигналами управления T и #OE. Функциональные блоки состоят из двух усилителей-формирователей с z-состояниями на выходах, схема включения обеспечивает разнонаправленную передачу.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.