Лабораторная работа 3.1. R– Sтриггер

Цель работы

Изучение различных схем RS-триггеров и их функционирования, приобретение навыков в определении характеристик триггеров.

Основные теоретические положения

Триггер (защелка) представляет собой устройство с двумя устойчивыми состояниями. Таблицы истинности RS-триггера и его разновидностей представлены в табл. 1. Файлы для моделирования RS-триггеров расположены в папке Lab_3_1\Модели.

Таблица истинности RS-триггеров Таблица 1

|

RS -триггер |

R -триггер |

S -триггер |

E -триггер |

|||||||||||

|

R |

S |

Qn+1 |

R |

S |

Qn+1 |

R |

S |

Qn+1 |

R |

S |

Qn+1 |

|||

|

0 |

0 |

Q n |

0 |

0 |

Q n |

0 |

0 |

Q n |

0 |

0 |

Q n |

|||

|

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|||

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

|||

|

1 |

1 |

– |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

Q n |

|||

По способу записи информации различают триггеры: асинхронные; синхронные.

У асинхронных триггеров запись информации осуществляется с поступлением информационного сигнала на его вход.

Асинхронный RS-триггер имеет два выхода: прямой Q и инверсный Q’ и два входа S(et) установка (Q=1) и R(eset) сброс (Q=0).

Выход триггера переходит в состояние Qn+1 =0, если S =0, R =1. При S =1, R =0 на выходе Qn+1 =1. Когда S =0, R =0 триггер сохраняет прежнее значение Qn. Комбинация сигналов S =1, R =1 запрещена, т.к. на прямом Q и инверсном Q’ выходе устанавливаются одинаковые значения, которые при переходе в режим хранения не сохраняются.

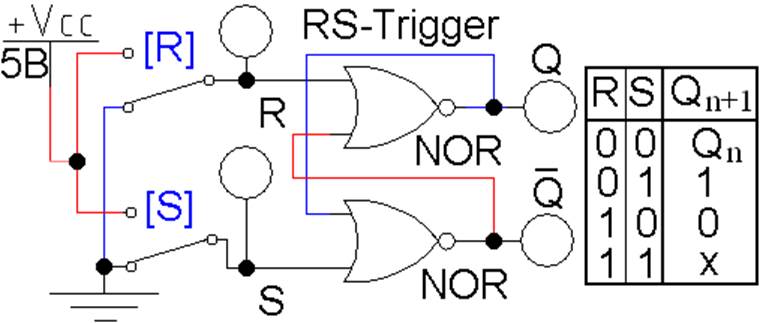

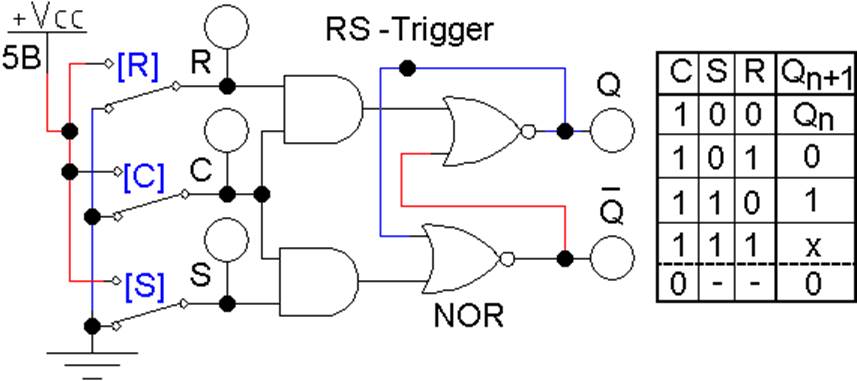

На рисунках 1, 2 изображены асинхронные RS-триггеры и их таблицы истинности.

Рис. 1 Схема RS-триггера на элементах 2ИЛИ-НЕ

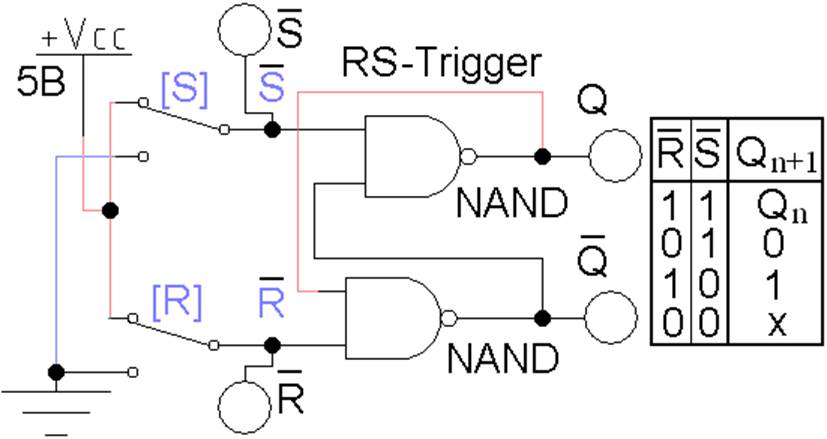

В синхронных триггерах, имеющих информационные и тактовые входы, запись осуществляется только при подаче разрешающего тактового импульса.

Рис. 2 Схема RS-триггера на элементах 2И-НЕ

Триггеры в виде логических компонентов расположены в поле элементов Digital(рис. 3).

Использование генератора слов позволяет проанализировать работу RS-триггера на всех наборах переменных.

Рис. 3 RS-триггер из поля элементов Digital

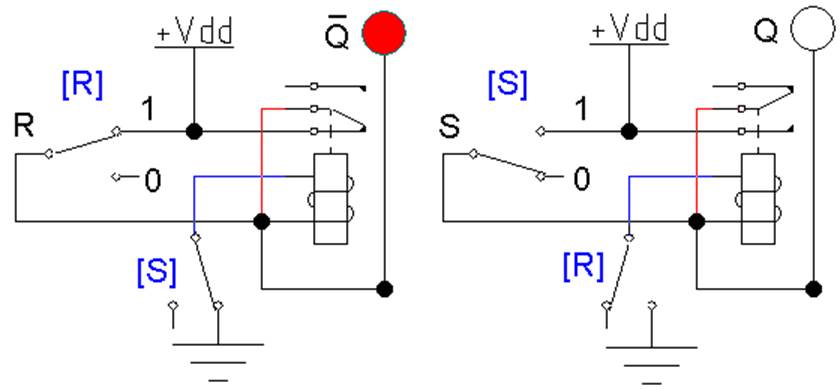

На рис. 4 изображен RS-триггер на реле, как вариант его реализации.

1 Приоритетные триггеры

Триггеры, у которых одни входы имеют преимущество над другими в установлении сигналов на выходе, называются приоритетными.

Такими устройствами, согласно таблице 1, являются R, S, E-триггеры. Последняя строка таблицы 1 определяет приоритет соответствующего входа.

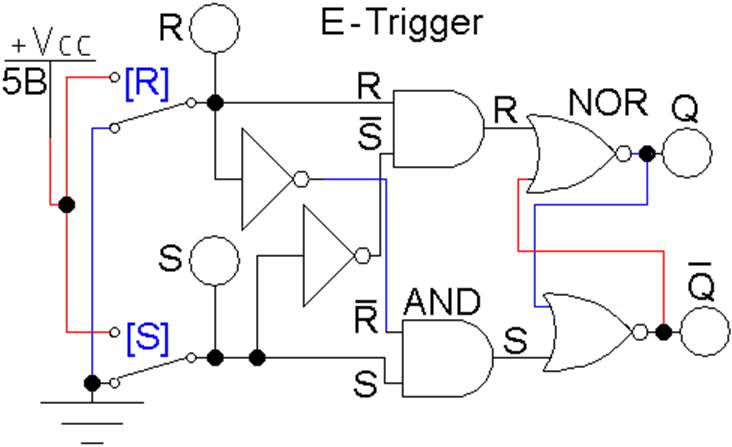

Приоритетным триггером является схема, представленная на рисунке 5.

Схема E триггера (рис. 5) устанавливает преимущество входного сигнала R или S, который появился на входе первым с помощью логической операции Импликация. Пришедший первым сигнал (логическая единица) инвертируется и устанавливает запрет на поступление сигнала на второй вход с помощью логической операции умножения.

Рис. 4 Схема RS-триггера на реле

Рис. 5 Схема Е-триггера

2 Синхронные триггеры

Запись информации в триггер (рис. 6) происходит при наличии на входе C=1.

Рис. 6 Синхронный RS-триггер

Триггер имеет потенциальный вход C. Запись информации происходит при наличии на входе C уровня логической единицы. При этом изменение состояния триггера связано с поступлением сигналов на входы R, S.

Задание 1

Подавая логические сигналы на входы триггеров (рис. 1…6) определить соответствующие логические сигналы на их прямом и инверсном выходе.

Задание 2

Определить наименование триггера (рис. 4), файл L3_RS_05.ewb. В таблице 2 оставить его правильное обозначение, остальные удалить.

Таблица задания 2 Таблица 2

|

Наименование триггера |

|||

|

RS |

R |

S |

E |

Задание 3

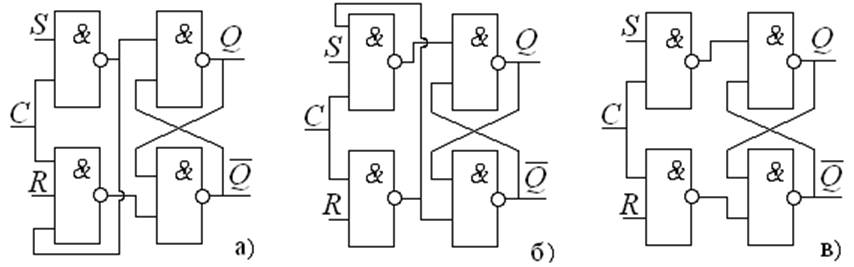

Определить, какие триггеры, собранные на основе RS-триггера, представлены на рис. 7. Оставить в таблице 3 правильные наименования триггеров, остальные удалить.

Рис. 7 Схемы триггеров

Таблица задания 3 Таблица 3

|

Триггер (рис. 7, а) |

Триггер (рис. 7, б) |

Триггер (рис. 7, в) |

|

Синхронный D |

Синхронный D |

Синхронный D |

|

Синхронный T |

Синхронный T |

Синхронный T |

|

Синхронный RS |

Синхронный RS |

Синхронный RS |

|

Асинхронный R |

Асинхронный R |

Асинхронный R |

|

Синхронный R |

Синхронный R |

Синхронный R |

|

Синхронный S |

Синхронный S |

Синхронный S |

|

Синхронный E |

Синхронный E |

Синхронный E |

Выводы

Триггеры являются ячейками памяти, куда заносится информация в двоичном коде, при необходимости информация считывается.

Простейшим является асинхронный RS триггер. На его основе создаются все более сложные триггеры.

Приоритетные триггеры позволяют исключить сбои и ошибки в работе различных устройств. Например, E-триггер исключает зажигание сигналов светофора одинакового цвета для различных направлений движения транспорта и т.д.

Простейшим примером триггера является выключатель освещения.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.