Лабораторная работа 2.4

Демультиплексоры

Основные теоретические положения

Демультиплексоромназывается комбинационное логическое устройство, предназначенное для управляемой передачи данных от одного источника X информации в несколько выходных каналов выходов Y согласно коду адреса A. Демультиплексор имеет один информационный вход, n адресных шин и m = 2n – выходов. Обозначение CD(1-m).

Файлы для моделирования этих элементов расположены в папке Lab_2_4\Модели.

|

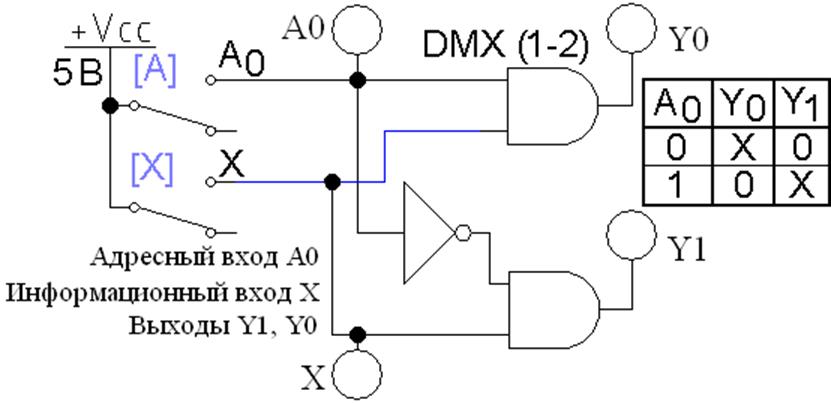

Для схемы DMX(1-2), рис. 1:

Рис. 1 Демультиплексор DMX(1-2), файл L2_DMX_01.ewb.

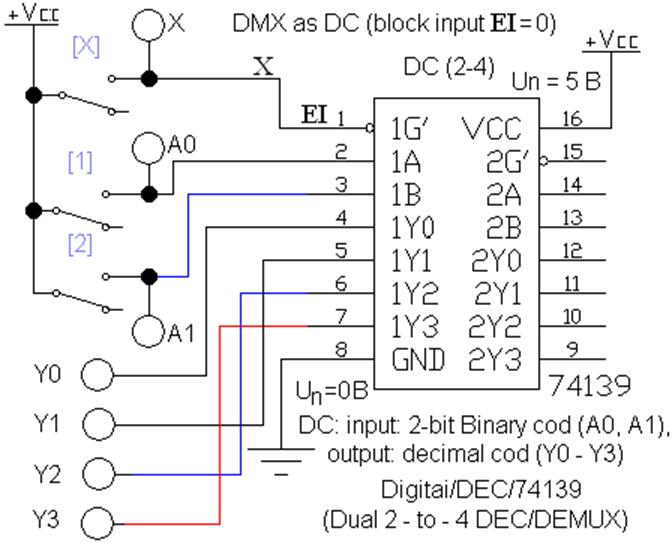

Рис. 2 Дешифратор – демультиплексор (2-4), файл L2_DMX_03.ewb.

Дешифратор – демультиплексор (рис. 2) в случае, если выключатель Х постоянно подключен к логическому нулю, работает как дешифратор. Когда с помощью данного выключателя подается двоичный код на информационный вход X, устройство работает как демультиплексор. В качестве входа X используется служебный вход EI.

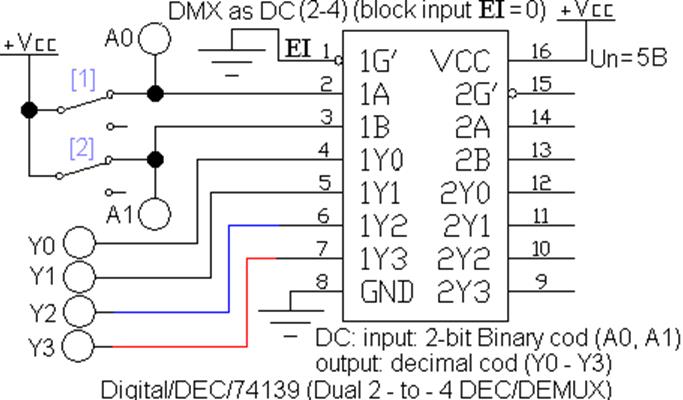

Применение демультиплексора как дешифратора представлено на рис. 3.

Рис. 3 Демультиплексор DMX(1-4) в качестве дешифратора DC(2-4), файл L2_DMX_04.ewb.

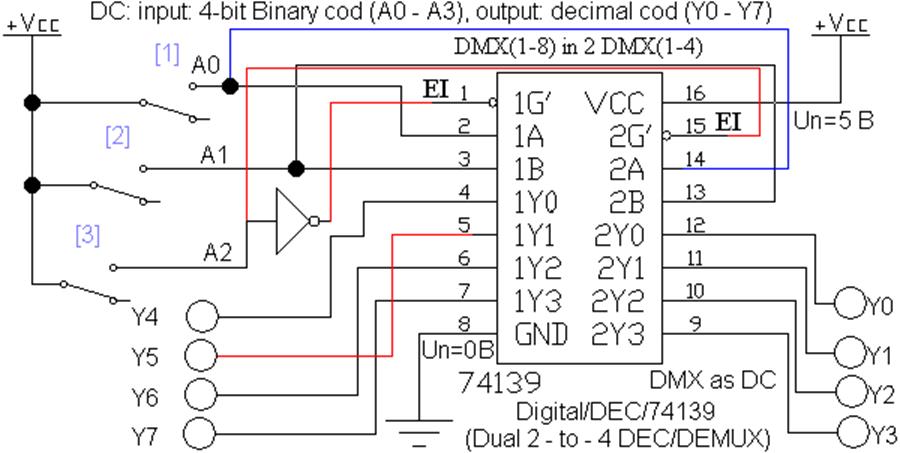

Увеличение разрядности демультиплексоров осуществляется аналогично дешифраторам за счет переключения двух DMX старшим разрядом входного адресного двоичного кода (рис. 4). В данной схеме DMX(1-8) используется два DMX(1-4) одной микросхемы. В качестве информационного входа использованы служебные входы EI. Адресные входы: A2, A1, A0, выходы: Y0, Y1…Y7. Демультиплексор может использоваться как дешифратор DC(3-8), если вход EI постоянно подключен к нулю.

Рис. 4 Демультиплексор DMX(1-8) на двух DMX(1-4), файл L2_DMX_05.ewb.

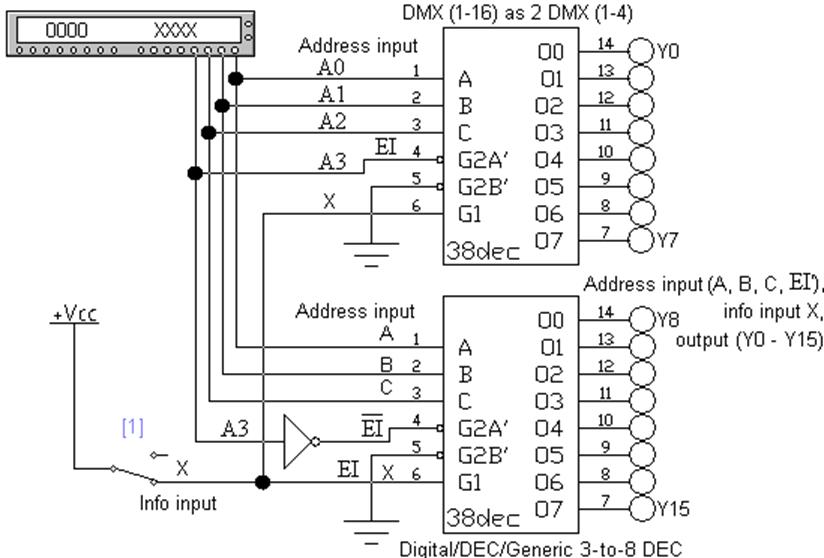

Аналогичное техническое решение использовано для создания DMX(1-16) на двух DMX(1-8), рис. 5.

Рис. 5 Демультиплексор DMX(1-16) на двух DMX(1-8), файл L2_DMX_07.ewb.

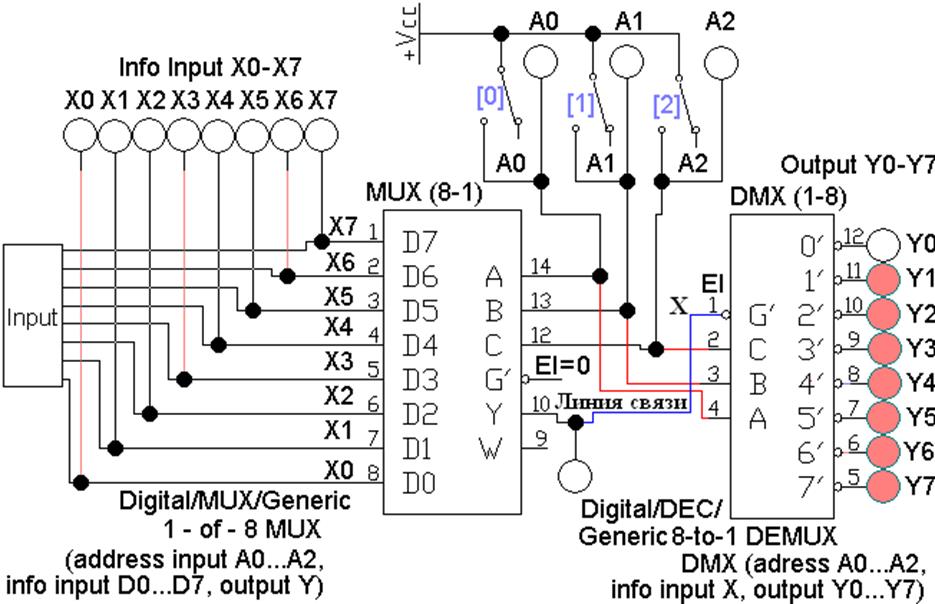

Для передачи данных по одному общему каналу с разделением во времени используются демультиплексоры и мультиплексоры (рис.6). Эти устройства выполняют по отношению друг к другу обратную функцию (файл L2_DMX_08.ewb).

Рис. 6 Связь с временным разделением восьми каналов в последовательном коде

на DMX(1-8) и мультиплексоре MUX(1-8)

Система (рис. 6) содержит: набор источников информации в двоичном параллельном коде (input), передатчик, преобразующий параллельный код в последовательный – мультиплексор MUX(8-1), на приемной части линии связи демультиплексор DMX(1-8) той же разрядности, преобразующий последовательный код в параллельный. Адресные коды устройств согласованы (A0…A2) и, соответственно, приемники (Y0…Y7) с передатчиками (X0…X7) информации. Пример использования: Интернет, сотовая связь и т.д.

Задание 1

Задавая комбинации входных сигналов, изучить работу демультиплексоров (рис. 1…6).

Задание 2

Для дешифратора – демультиплексора (2-4), рис. 2 (файл L2_DMX_03.ewb) составить таблицу истинности (табл. 1) его работы как демультиплексора, а также в качестве дешифратора, задав соответствующее значение переменной X (табл. 2).

Таблица истинности DMX Таблица 1

|

Входы |

Выходы |

||||

|

A1 |

A0 |

Y3 |

Y2 |

Y1 |

Y0 |

|

0 |

0 |

||||

|

0 |

1 |

||||

|

1 |

0 |

||||

|

1 |

1 |

||||

Таблица истинности DС Таблица 2

|

Входы |

Выходы |

|||||

|

X |

A1 |

A0 |

Y3 |

Y2 |

Y1 |

Y0 |

|

0 |

0 |

|||||

|

0 |

1 |

|||||

|

1 |

0 |

|||||

|

1 |

1 |

|||||

|

Х |

Х |

|||||

Символ «Х» обозначает любое значение переменной, которое не оказывает влияния на результат.

Задание 3

Для модели системы связи (рис. 6), файл L2_DMX_08.ewb, заполнить табл. 3. Требуется записать номера соединяемых линий X0...X7 (параллельный код) с линиями Y0...Y7 в соответствии с указанным адресным кодом A (одна линия X c одной линией Y).

Таблица истинности системы связи Таблица 3

|

№ |

A2 |

A1 |

A0 |

НомерX |

НомерY |

|

1 |

0 |

0 |

0 |

||

|

2 |

0 |

0 |

1 |

||

|

3 |

0 |

1 |

0 |

||

|

4 |

0 |

1 |

1 |

||

|

5 |

1 |

0 |

0 |

||

|

6 |

1 |

0 |

1 |

||

|

7 |

1 |

1 |

0 |

||

|

8 |

1 |

1 |

1 |

Задание 4

В таблице 4 приведены уравнения, которые используются для увеличения разрядности демультиплексоров. Удалить уравнение, которое не соответствует схеме демультиплексора, файл L2_DMX_05.ewb (рис. 4).

Таблица уравнений для увеличения разрядности Таблица 4

|

№ |

Уравнения |

|

1 |

|

|

2 |

|

Выводы.

Демультиплексор:

- может работать в качестве дешифратора;

- является основным элементом систем связи с временным разделением;

- используется для согласования работы устройств компьютера (микропроцессор, память и т.д.), т.к. они содержат мультиплексоры для снижения числа выводов микросхем и обмениваются информацией аналогично системам связи с временным разделением.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.