SiЭЛ — площадь i-го элемента ИС, равная площади соответствующего кармана, мм2.

Для увеличения РУП необходимо уменьшать площадь элементов и толщину изолирующих прослоек между ними, а для увеличения КИСП необходимо уменьшить толщину изолирующих прослоек между карманами. Как видно из рис.8 и 15, площадь МОП-транзистора в несколько раз меньше площади биполярного транзистора. Кроме того, в МДП-ИС не используются ДР и ДК, площади которых могут во много раз превосходить площадь транзистора. Как было показано на рис.2, в МДП-ИС не требуется также специальная изоляция между элементами. В результате отмеченных особенностей РУП для МДП-ИС примерно в 5 раз больше, чем в БТ-ИС, что и обуславливает, наряду с простой технологией, существенно более низкую стоимость МДП-ИС. Это же обстоятельство определяет значительно более высокую степень интеграции МДП-ИС. Несмотря на это, МДП-ИС не могут полностью вытеснить БТ-ИС, поскольку последние обладают более высоким быстродействием и более широкой полосой частот, что может быть решающим условием при выборе типа ИС.

2. Задание для самостоятельной работы

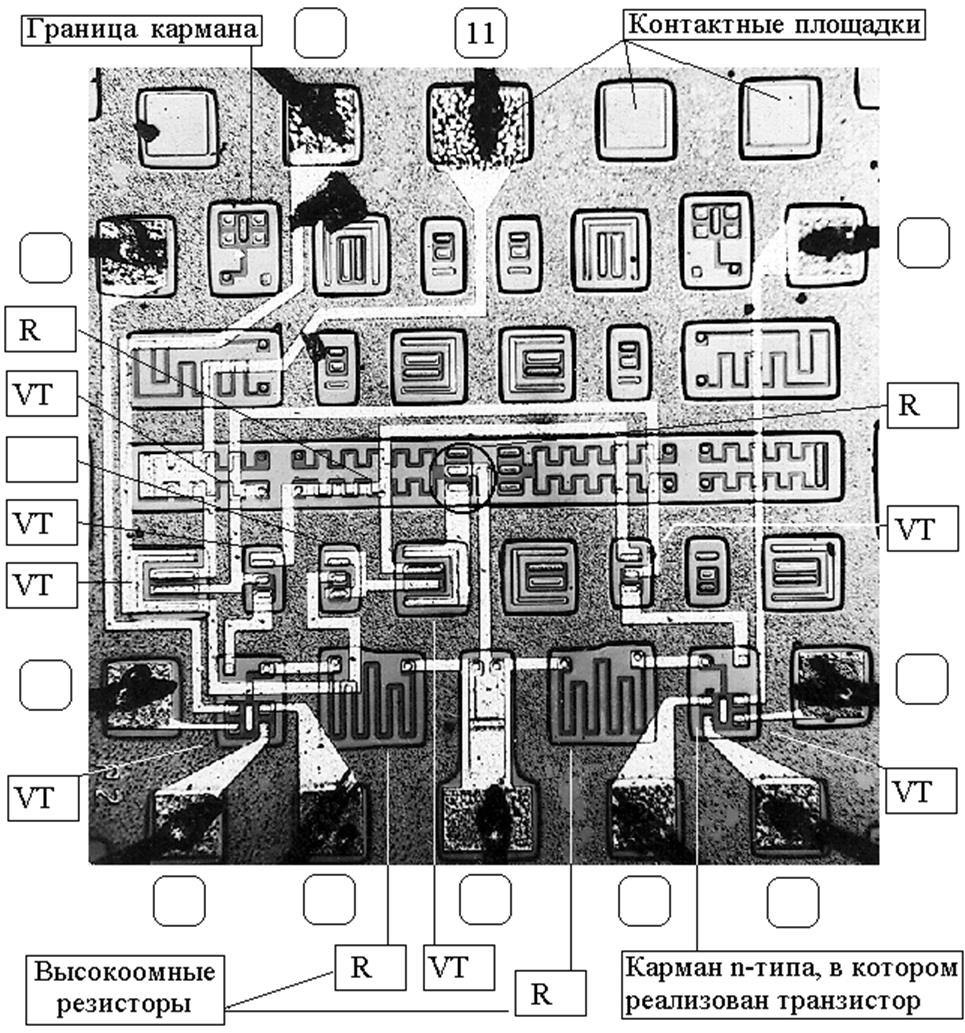

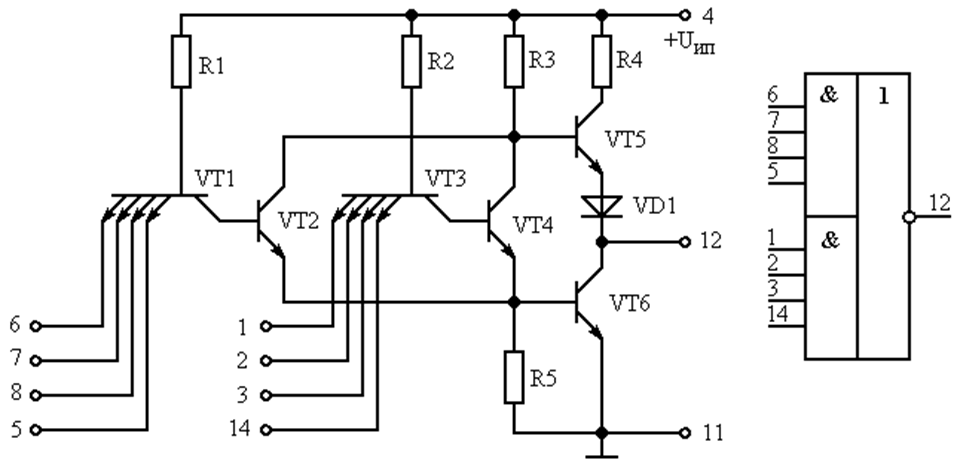

На рис. 17 приведена фотография топологии полупроводниковой ИС 134ЛР4. Фотография выполнена в масштабе 100:1. На рис. 18 приведена принципиальная электрическая схема этой микросхемы.

Требуется:

а) изучить принципиальную электрическую схему и топологию ИС по фотографии, найти на топологии каждый элемент ИС в соответствии со схемой, определить степень интеграции ИС;

б) зная масштаб изображения ИС на фотографии с помощью измерительной линейки определить размеры подложки ИС;

в) нарисовать на миллиметровой бумаге фрагмент топологии ИС, содержащий транзистор, резистор или конденсатор и контактную площадку; топология должна быть нарисована с соблюдением конфигурации и размеров элементов, размер рисунка должен быть не менее 160х160 мм; области полупроводника с различными типами проводимости ( коллектора - “кармана”, базы, эмиттера, изолирующих перемычек) и монтажные линии должны быть выделены разным цветом;

г) на втором рисунке нарисовать структуру элементов, попавших в плоскости разреза, следы которых должны быть отмечены на топологии; в плоскости разреза элементы должны быть окрашены в такие же цвета, что и на топологии; размеры элементов в горизонтальном направлении должны соответствовать топологии, а в вертикальном — устанавливаются, исходя из данных, приведенных в разделе “Теоретическая часть” пособия (см табл. 1, 2 и 3 ).

Рис 17. Фотография топологии полупроводниковой ИС 134ЛР4

в масштабе 100:1

а) б)

Рис 18. Принципиальная электрическая схема микросхемы 134ЛР4 (а)

и ее условное обозначение

3. Контрольные вопросы

1. Дайте классификацию ИС по степени интеграции, конструктивно-технологическим признакам, функциональному значению и применяемости.

2. Перечислите особенности полупроводниковых ИС на основе биполярых транзисторов и МОП-транзисторов.

3. Перечислите особенности тонкопленочных и толстопленочных ГИС.

4. Как выполняется диодная изоляция при эпитаксиально-планарной технологии?

5. Как выполняется диодная изоляция при методе коллекторной диффузии?

6. Нарисуйте структуру n-p-n транзистора, полученного по изопланарной технологии и укажите особенности изоляции.

7. Нарисуйте структуру n-p-n транзистора, полученного по технологии “кремний на сапфире”.

8. Как выполняется изоляция элементов при “эпик-процессе”.

9. Нарисуйте структуру биполярного транзистора, выполненного по изопланарной технологии; укажите его достоинства и недостатки.

10. Нарисуйте структуру вертикального p-n-p транзистора, изготовленного по эпитаксиально-планарной технологии одновременно с n-p-n транзистором.

11. Нарисуйте структуру многоэмиттерного n-p-n транзистора и обоснуйте целесообразность его применения.

12. Нарисуйте структуру паразитного и горизонтального p-n-p транзистора и укажите их достоинства и недостатки.

13. Дайте сравнительную характеристику различных схем диодного включения транзистора, применяемых для реализации интегрального диода.

14. Нарисуйте структуру ДР на основе базового и эмиттерного слоя и дайте их сравнительную характеристику.

15. Нарисуйте структуру полупроводникового резистора, полученного по технологии ионного внедрения и укажите его достоинства перед ДР.

16. Нарисуйте структуру ДК и МОП-конденсатора и сравните их между собой.

17. Что такое плотность упаковки элементов ИС и как она определяется?

18. Что такое коэффициент использования площади подложки и как он определяется?

19. Почему в МДП-ИС выше плотность упаковки элементов ИС и коэффициент использования площади подложки, чем БТ-ИС?

20. Почему МДП-ИС имеет меньшую стоимость, чем БТ-ИС?

Уровень подготовки по рассмотренному разделу курса “Электронные твердотельные приборы и микроэлектроника” считается достаточным, если студент:

а) изучил особенности топологии и структуры полупроводниковых и МДП ИС и их элементов в объеме раздела “Теоретическая часть“ данного учебного пособия и соответствующих разделов указанной ниже литературы;

б) изучил топологию интегральной микросхемы и сопоставил ее с принципиальной электрической схемой;

в) может нарисовать любой элемент микросхемы в разрезе;

в) может ответить на любой вопрос из раздела 3.

Библиографический список

1. Аваев Н.А., Наумов Ю.И., Фролкин В.Т. Основы микроэлектроники. М.:Радио и связь, 1991. 288 с.

2. Аналоговая и цифровая электроника: Учебник для вузов/ Ю.Ф. Опадчий, О.П. Глудкин, А.И. Гуров; Под ред. О.П. Глудкина. М: Радио и связь, 1996. - 768 с.

3. Степаненко И.П. Основы микроэлектроники. М.: Сов. радио, 1980. 424 с.

4. Ефимов И.Е., Козырь И.Я. Основы микроэлектроники. М.: Высшая школа, 1983. 384 с.

ИССЛЕДОВАНИЕ ТОПОЛОГИИ И СТРУКТУРЫ

ИНТЕГРАЛЬНЫХ МИКРОСХЕМ.

Составитель Семенов Борис Владимирович

Редактор

---------------------------------------------------------------------------------

Подписано в печать Формат 60х84 1/16

Бумага типографская Офсетнаяая печать Усл.п.л.

Уч.-изд.л. Тираж Заказ Цена

-------------------------------------------------------------------------------

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.