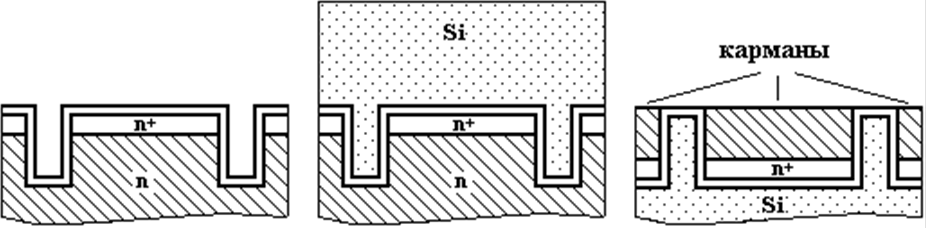

Более сложным вариантом диодной изоляции является изоляция коллекторной диффузией ( ИКД, рис.5). В этом случае применяется эпитаксиальный слой p-типа толщиной 2-3 мкм, под которым расположены скрытые n+-слои, сформированные на поверхности исходной пластины p-типа до эпитаксии. Изоляция осуществляется диффузией донорных примесей до встречи со скрытым n+-слоем. В результате получаются карманы p-типа ( будущие базовые области ), а скрытый n+-слой вместе с разделительными n+-стенками образует область коллектора. Достоинства ИКД метода заключается в увеличении коэффициента использования площади подложки из-за малой толщины изолирующих стенок. Недостатками ИКД метода являются меньшее пробивное напряжение и большая емкость коллектора, а также необходимость проведения дополнительной диффузии акцепторной примеси в p-карманы для создания ускоряющего поля в базе.

Этапы получения диэлектрической изоляции при классическом эпик-процессе показаны на рис.6. Исходная пластина n - кремния покрывается тонким (2-3 мкм) эпитаксиальным n+- слоем (для формирования

Рис.6. Метод диэлектрической изоляции ( эпик-процесс ).

скрытого слоя ). На n+-слое формируется маска из SiO2, через которую в пластине вытравливаются канавки глубиной 10-15 мкм. После этого рельефная поверхность окисляется и на слой SiO2 напыляется толстый (200-300 мкм) слой поликристалла Si. Далее исходную n-пластину сошлифовывают до вскрытия дна канавок и получают n-карманы со скрытым n+-слоем, окруженные снизу и с боков изолирующим слоем SiO2. Основная трудность описанного процесса заключается в прецизионной шлифовке n-пластины толщиной 200-300 мкм с допустимой погрешностью не более 1-2 мкм по всей поверхности пластины диаметром до 80 мм.

В настоящее время большое распространение получает разновидность диэлектрической изоляции — технология “кремний на сапфире” ( КНС ). На сапфировой пластине, имеющей аналогичную с Si структуру кристаллической решетки, наращивается слой n-кремния. В дальнейшем в этом слое протравливаются бороздки до сапфира, в результате чего образуются n-островки, изолированные снизу сапфиром, а с боков - воздухом. Недостатком технологии КНС - рельефность поверхности ИС, затрудняющая осуществление металлической разводки.

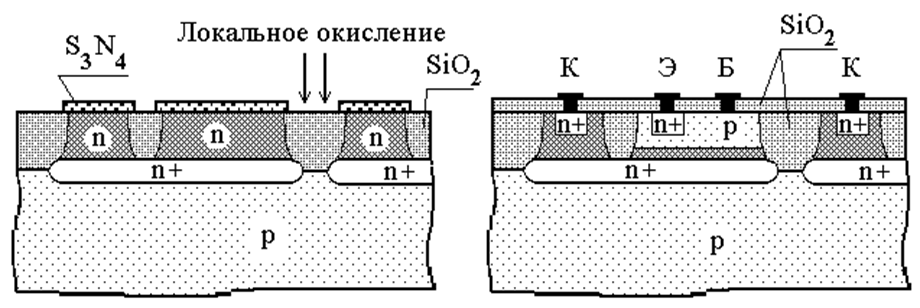

Применяются также комбинированные методы изоляции, сочетающие в какой-то мере положительные качества диодного и диэлектрического методов. Наиболее распространенным комбинированным методом является изопланарная технология (рис.7). В ее основе лежит локальное сквозное прокисление (через маску из нитрида кремния) тонкого (2 мкм) эпитаксиального слоя n-кремния, наращенного на пластину p-кремния после формирования скрытых n+-слоев. Полученные в результате n-карманы ( рис.7,а) имеют диэлектрические ( из SiO2) стенки, а не полупроводниковые, как в случае эпитаксиально-планарной технологии. Каждый карман окислом делится на две части: главную и вспомогательную, связанные через скрытый n+-слой.

а). б).

Рис.7. Изопланарная технология

В главной части формируется транзистор с выводами базы и эмиттера, а в другой части формируется вывод коллектора ( рис.7,б ). Благодаря такой структуре резко уменьшается коллекторная емкость транзистора, что улучшает его частотные характеристики, а также повышается плотность компоновки элементов, т.е. коэффициент использования площади пластины.

Вторая особенность интегральных элементов приводит к тому, что при их изготовлении остается меньше свободы выбора, чем при изготовлении дискретных аналогов. В БТ-ИС за основу взята структура n-p-n транзистора, что объясняется ее большей граничной частотой ( из-за большей подвижности электрона ) и более высоким коэффициентом передачи тока ( из-за большей степени легирования n+-эмиттера ). Поскольку n-p-n транзистор является основным, то параметры диффузионных слоев ( глубина, степень легирования ) выбираются исходя из требований, предъявляемых к его параметрам. Структура и технология других элементов (диодов, резисторов, конденсаторов, p-n-p транзисторов) должны “приспосабливаться” к технологии n-p-n транзистора. Это означает, что при их изготовлении следует по возможности избегать дополнительных технологических операций и для формирования их структур ограничиваться теми же рабочими слоями ( коллекторный, базовый, эмиттерный ). Рассмотрим основные типы структур элементов Бт-ИС.

1.3.2. Элементы БТ-ИС

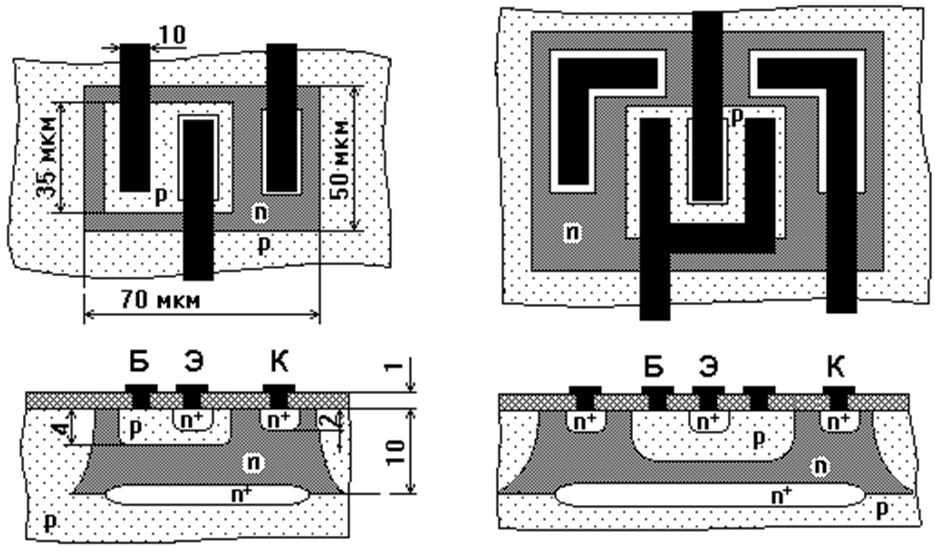

На рис.8 приведены типичные варианты топологии и соответствующие вертикальные разрезы n-p-n транзистора с указанием ориентировочных размеров элементов структуры.

Рис. 8. Топология и вертикальный разрез типичных вариантов

интегральных n-p-n транзисторов

Типичные параметры слоев интегрального транзистора приведены в табл.1.

Параметры слоев интегрального транзистора Таблица 1

|

Наименование слоя |

Концентрация примесей, см-3 |

Толщина слоя d, мкм |

Удельное сопротивление слоя Rs, Ом/ |

|

Подложка p-типа |

1,5* 1015 |

300 |

— |

|

Скрытый n+-слой |

1018 |

5 — 10 |

8 - 20 |

|

Коллекторный n-слой |

5*1015 |

10-15 |

500 |

|

Базовый p-слой |

1016 (макс) |

2,5 |

200 |

|

Эмиттерный n+-слой |

1021 (макс) |

2 |

5-15 |

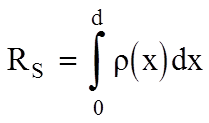

Удельное сопротивление слоя RS определяется как продольное сопротивление слоя квадратной конфигурации и вычисляется по формуле

(2)

(2)

где r(x) - удельное сопротивление полупроводника в плоскости, расположенной на расстоянии x от границы;

d - толщина слоя.

При указанных параметрах слоев транзисторы имеют коэффициент b=100-200 и ¦T = 200—500 Мгц.

В БТ-ИС применяются разновидности n-p-n транзисторов (многоэмиттерный, многоколлекторный и т.д.), не выпускаемые в виде дискретных приборов. Структура многоэмиттерного транзистора (МЭТ) показана на рис.9. МЭТ составляет основу весьма распространенного класса цифровых ИС, построенных по транзисторно-транзисторной логике (ТТЛ), и в первом приближении может рассматриваться как совокупность отдельных транзисторов, базы и коллекторы которых соединены в две общие шины. Применение МЭТ позволяет увеличить плотность упаковки элементов БТ-ИС, т.к. МЭТ с n-эмиттерами (n » 5-10) занимает меньшую площадь, чем n отдельных транзисторов. Для исключения транзисторного эффекта между двумя эмиттерами расстояние между ними выбирается примерно в 5 раз больше диффузионной длины носителей в базовом слое. Для уменьшения инверсного коэффициента ai омический базовый контакт удален от активной области транзистора и соединен с ней с помощью узкого “перешейка” с сопротивлением 200-300 Ом.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.