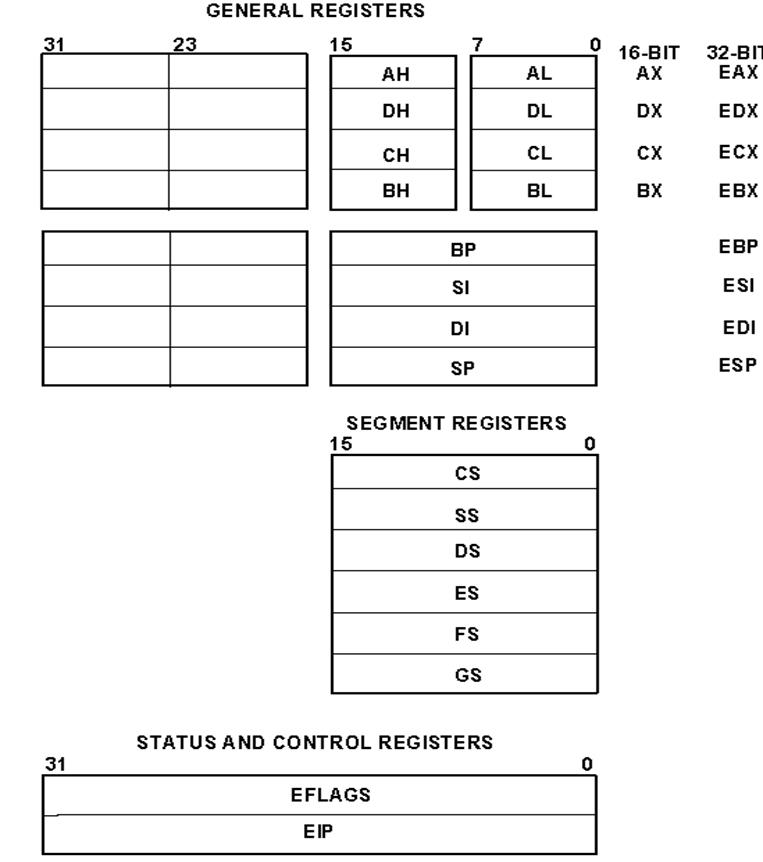

1) Регистры данных ) – (E)AX, (E)BX,(E)CX, (E)DX (в некоторых книгах их называют регистрами общего назначения. Операнды в этих регистрах могут представлять собой 32 или 16- разрядное слово или байт. Если операнд - байт, может быть указан один из двух младших байтов регистра (*H или *L). Есть ряд команд, в которых функции отдельных регистров специализированы.

2) Адресные регистры (E)SI, (E)DI,(E)BP, (E)SP (используются для хранения 32 или 16-разрядных адресов, байтовый доступ к частям этих регистров невозможен). Адресные регистры во многих командах также специализированы.

3) Сегментные регистры сегмент команд CS, сегмент стека SS и четыре сегмента данных - DS и ES (в реальном режиме процессора указывают начала четырех сегментов - участков по 64 К байт в 1М адресном пространстве памяти).

4) Счетчик команд (в оригинале – указатель команд, Instruction Pointer (E)IP) и Регистр флагов EFLAGS.

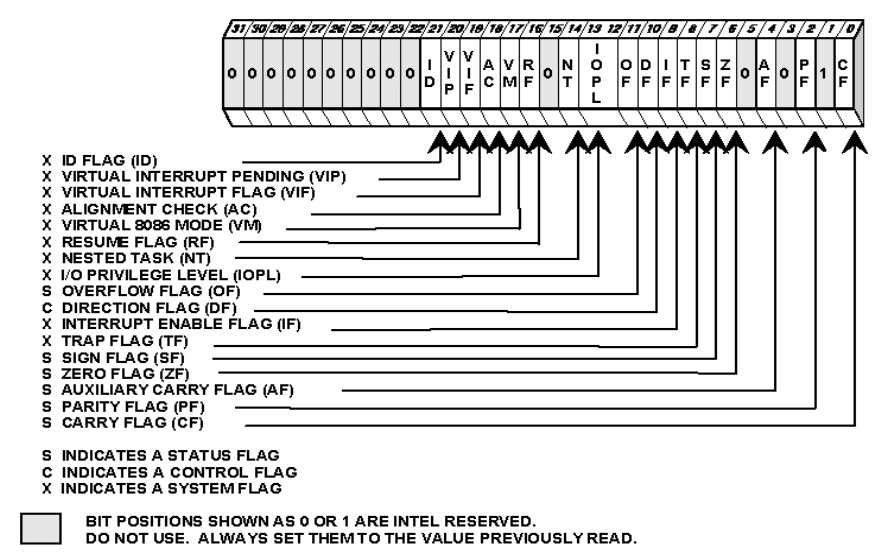

Формат регистра флагов приведен на рисунке.

Младшие 12 битов этого регистра используются в реальном режиме (см. далее этот подраздел), остальные поля (биты) регистра состояний используются в защищенном режиме.

Программная модель процессора х86 (как количество и назначение регистров, так и структура регисра состояний) достаточно сложна. В младших моделях семейства х86 назначение регистров было в сильной степени специализировано.

AX Аккумулятор Умножение, деление и

ввод-вывод слов

AL Аккумулятор(мл) Умножение, деление и

ввод-вывод байтов

AH Аккумулятор(ст) Умножение и деление

байтов

BX Регистр базы Базовый регистр,

может быть использован как адресный

CX Счетчик Операции с

цепочками, циклы

CL Счетчик (мл) Динамические сдвиги

и ротации

DX Данные Умножение и

деление слов, косвенный ввод-вывод

SP Указатель стека Стековые операции

BP Указатель базы Базовый регистр

SI Индекс источника Операции с цепочками,

индексный регистр

DI Индекс приемника Операции с цепочками,

Начиная с процессора i386 специализация регистров была в значительной степени исключена, структура регистровой модели стала более «ортогональной».

Регистр флагов

процессоров х86 в реальном режиме

|

15 |

11 |

10 |

9 |

8 |

7 |

1 |

0 |

||||||||

OF |

DF |

IF |

TF |

SF |

ZF |

0 |

AC |

0 |

PF |

0 |

CF |

CF ( Carry

Flag ) - флаг переноса;

PF ( Parity Flag ) - флаг

четности;

AF ( Auxiliary Carry Flag ) - флаг вспомогательного переноса;

ZF ( Zero Flag ) - флаг нуля;

SF ( Sign Flag ) - флаг знака;

TF ( Trap Flag ) - флаг прерывания для отладки

IF ( Interrupt-Enable Flag ) - флаг разрешения прерывания;

DF ( Direction Flag ) - флаг направления цепочечных (строковых) команд

OF ( Overflow Flag ) - флаг переполнения.

Подробнее назначение и использование флагов мы будем рассматривать позже.

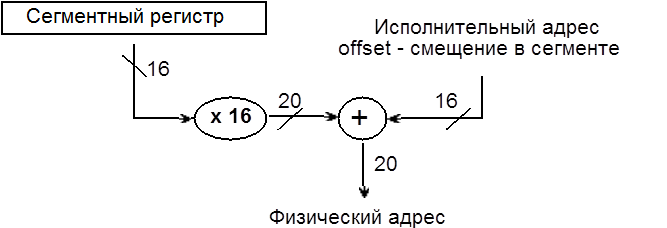

Сегментные регистры - используются при вычислении физического адреса при обращении к внешней памяти. Использование сегментного механизма в 8086 - пример того, как в 16-разрядной архитектуре преодолевался 64K-барьер размера адресного пространства.

Исполнительный адрес (буквальный перевод словосочетания executive address) в реальном режиме - 16-битовый результат работы схемотехники адресной арифметики (при обращении к операнду - в соответствии с используемым в команде способом адресации).

Вопрос для любопытных: что произойдет, если при сложении возникнет переполнение разрядной сетки?

Один и тот же физический адрес можно получить, имея несколько (сколько?) комбинаций значений сегмента и смещения

CS - задает сегмент команд (command segment), из которого производится выборка команд.

DS, ES - два сегмента данных, к одному из них производится обращение при выборке операндов. Какой именно сегмент используется, зависит от вида команды (чаще всего обращение происходит к сегменту DS, хотя программист может в большинстве случаев явно указать в команде, какой сегмент следует использовать (см. префикс переназначения сегмента). В процессорах начиная с 386, количество сегментов увеличилось до 6 за счет добавления еще двух сегментов данных FS и GS.

SS - сегмент стека, к нему происходит обращение при операциях со стеком. (О стековой адресации см. раздел Способы адресации).

Регистровая модель прикладного и системного программиста для процессоров Itanium (архитектура IA-64) описана ЗДЕСЬ (структура регистровой модели – рис. на стр. 35 по сквозной нумерации).

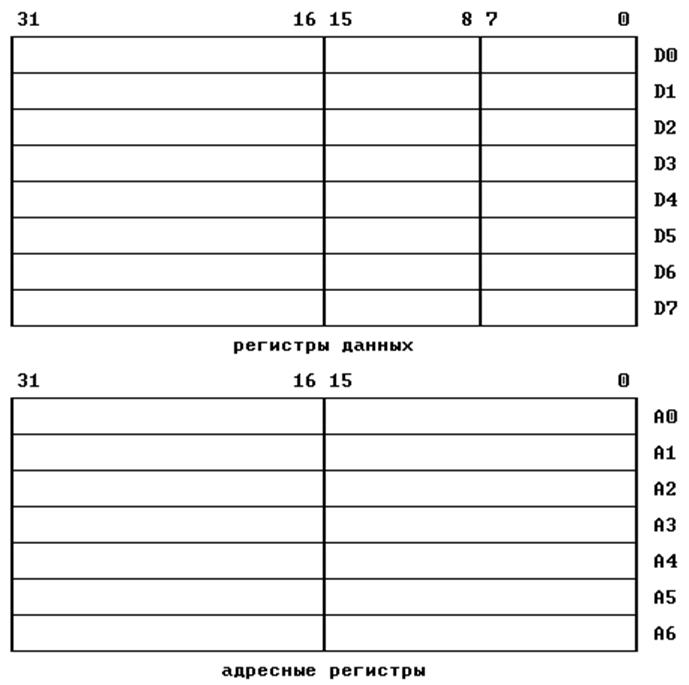

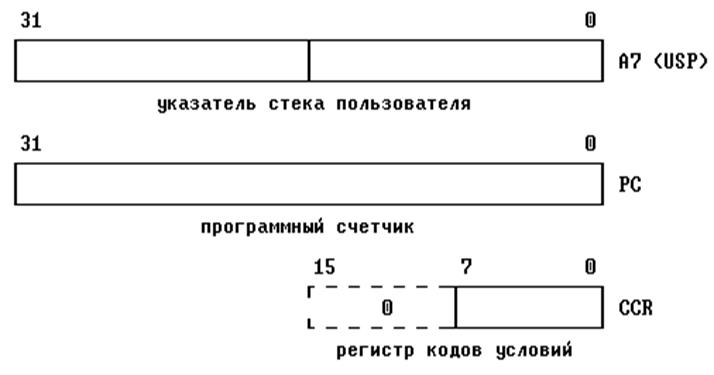

Полную информацию по архитектуре M68x00 (фирма называет вычислительное ядро аббревиатурой CPU32) можно получить, например, в документе 68360um.pdf, раздел 5 CPU32+.

Эта структура отличается высокой степенью симметрии (ортогональности). Регистровая модель содержит 8 равноправных регистров данных D0… D7 и 8 адресных регистров A0…A7, из которых регистр A7 используется как указатель стека. Этот регистр существует в двух экземплярах, один используется в пользовательском режиме, второй в системном режиме.

Структура регистра состояний процессоров 68х изображена на рисунке.

Регистровую модель MCS-51 следует рассматривать одномвременно с изучением структуры адресных пространств памяти.

Аккумулятор (A, Acc) – 8 бит

Регистр B ‑ 8 бит

Data Pointer DP ‑ 16 бит, доступный байтами: DPL – младшая половина, DPH – старшая. Это адресный регистр.

Указатель стека ‑ 8 бит.

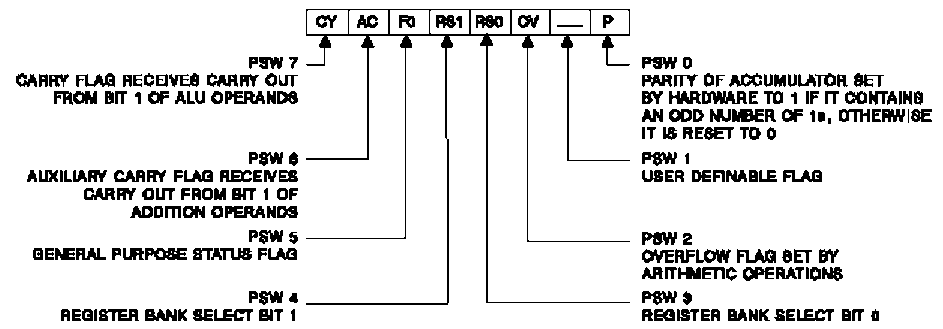

Регистр слова состояния программы (Program Status Word PSW)

Четрые банка регистров, по 8 однобайтовых регистров в каждом банке.

Задание для самостоятельного выполнения:

Во всем мире множество фирм выпускает (легально, по лицензии, или разрабатывая аналоги самостоятельно) однокристальные ЭВМ (ОЭВМ) с архитектурой фирмы Intel MCS51. Познакомьтесь с программной моделью процессоров семейства MCS51 (например, по источнику \Docs\Atmel\AT89S8252\Doc0497_обзор_архитектуры.pdf – это документация по однокристальной микроЭВМ фирмы Atmel). Можно также использовать книгу Сташин В.В., Урусов А.В., Мологонцева О.Ф. Проектирование цифровых устройств на однокристальных микроконтроллерах. М.: Энергоатомиздат, 1990. – это описание российского аналога - 1816ВЕ51

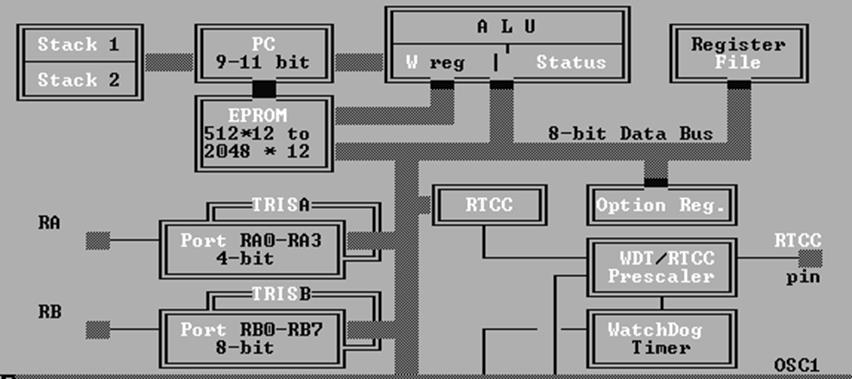

Подробно можно познакомиться с ней, запустив обучающую программу PicMan ОТСЮДА.

Регистровая модель процессора PIC16C5x выглядит приблизительно так: (см. рис.).

Основные ее особенности:

АЛУ содержит регистр-аккумулятор W (Working Register) который участвует в большинстве команд в качестве операнда. Таким образом, PIC-процессор ‑ типичный образец процессора «с аккумулятором».

Память программ и память данных разделены, таким образом, PIC‑процессор это типичный пример гарвардской архитектуры.

[АПН1] Куча понятий используется, которые пока еще не определены.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.