3) по адресной информации, которая содержится в команде, вычисляется адрес операнда (может быть адреса нескольких операндов), при этом для определения значения адреса операнда, возможно, придется выполнить дополнительные обращения к памяти

4) операнд(ы) извлекае(ю)тся из места своего расположения (из регистра(ов) или из памяти)

5) в соответствии с кодом операции, содержащимся в команде, выполняется действие (например, вычисляется сумма двух операндов)

6) результат действия помещается (в память или в регистр) в соответствии с адресной информацией, содержащейся в команде

Отметим некоторые особенности этой структуры, существенные для понимания работы процессора:

а) Какими должны быть следующие этапы выполнения команды, можно решить, только выполнив некоторые предыдущие. Так например, только после выполнения декодирования можно определить, как использовать адресную часть. С другой стороны, даже если последующая команда использует результат, формируемый текущей командой, в последующей команде можно выполнить первых три шага независимо от того, закончилось ли выполнение текущей.

б) При выполнении команды происходит одно или несколько обращений к памяти.

В качестве основной (массовой) памяти используется главным образом динамическая полупроводниковая память, скорость работы которой невелика по сравнению с процессором, и которая из-за этого часто является "узким местом" замедляющим работу системы. Поэтому рассмотрим процесс обращения к памяти несколько подробнее.

Процесс обмена между частями вычислительной системы является циклическим, причем в одном цикле происходит передача порции данных, размер которой не превышает разрядности шины данных[АПН1] . Цикл состоит из двух последовательных операций:

1) Передача из процессора в память адреса

2) Передача данных по выбранному адресу

В настоящее время для динамической памяти длительность цикла памяти составляет 60...70 нс. Длительность канального цикла определяется типом шины (канала, магистрали) в компьютере.

Рассмотрим теперь регистровые (программные) модели нескольких различных процессоров.

Понятие «модель устройства для программиста», «программная модель» (Programming Model) «регистровая модель» (процессора, но может быть и другого цифрового программно управляемого устройства) обозначает совокупность всех программно-доступных (синоним – «программно-видимых») элементов этого (программируемого) устройства, состояние (содержимое) которых программист может проанализировать (прочитать) или изменить командами программы.

Понятие применимо как к процессору, так и к другим узлам вычислительной системы (например к периферийным устройствам: программная модель таймера, контроллера дисков и т.п.).

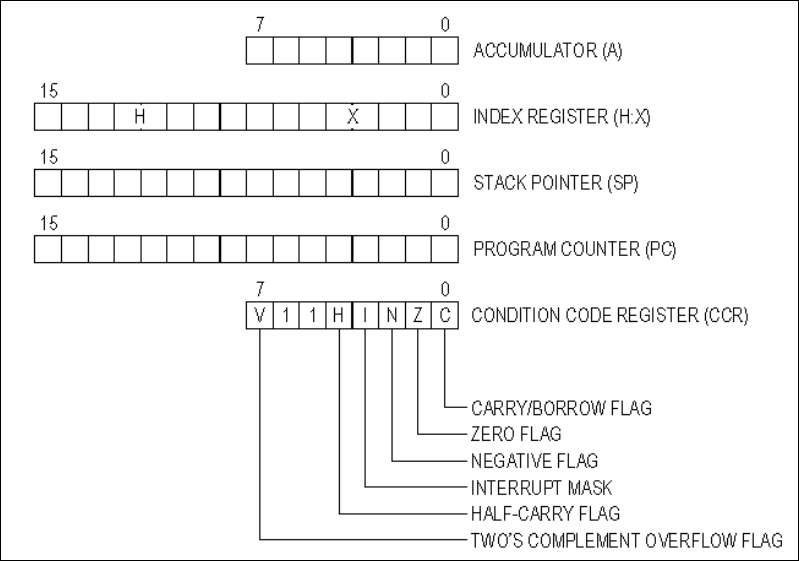

Подробно познакомиться с процессором можно по документу HC08. MC68HC908AB32 HCMOS Microcontroller Unit, Раздел 7 (Section 7 Central Processor Unit).

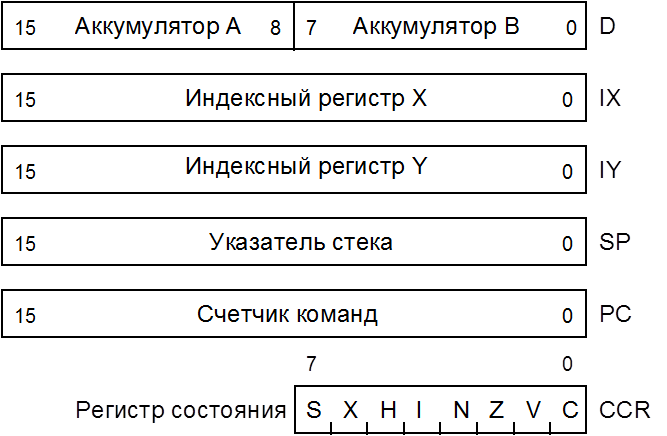

Вы можете получить подробности о свойствах процессора M68НС11 из документа M68HC11 Reference Manual, Motorola , а о процессоре M68HC12 – из документа 12CPURM.pdf (регистровая модель изображена на рис.2.1, стр. 15).

Эти два 8-битовых регистра

используются как источники операндов и/или приемники результата

операции при выполнении большинства команд обработки данных. Некоторые команды

используют эти два 8-битовых регистра как один 16-битовый регистр, в этом

случае его называют "сдвоенным аккумулятором" и используют

мнемоническое обозначение D.

В большинстве команд можно использовать равным образом как регистр A

так и регистр B.

Эти регистры используются для хранения компонент адреса при использовании индексной адресации. Более ранние модели контроллеров (семейства M6800 и M6801) содержали только один адресный (индексный) регистр IX.

Стек может быть расположен в любом месте 64К адресного пространства и может быть любого размера в пределах имеющейся в системе памяти. Запись в стек производится с постдекрементом SP, а считывание из стека - с преинкрементом, т.е. при записи содержимое SP уменьшается после записи в стек, а при считывании - увеличивается до считывания из стека. В любое время SP содержит адрес первой свободной ячейки стека. При записи в стек двухбайтовых элементов данных вначале записывается младший байт. а затем старший (при этом старшие байты оказываются в младших адресах - в процессорах Intel - наоборот !). При обработке запроса прерывания в стек записываются все (!) регистры процессора, на что в стеке требуется 9 байтов, а при выполнении - 9 циклов процессора.

16-битовый счетчик команд всегда содержит адрес следующей команды, размер адресного пространства, которое разделают программный код и данные, равно 64 кбайт.

Он содержит пять битов флагов (признаков), меняющих свое состояние в зависимости от результатов предыдущих операций: C,V,Z,N,H, два бита маскирования прерываний I,X и бит Sзапрета выполнения команды останова STOP.

Признаки Carry, oVerflow, Zero, Negative. Half-carry - аналогичны имеющимся в других процессорах, однако меняют свое состояние при выполнении подавляющего большинства команд, и в частности при пересылках (в отличие от процессоров Intel). Это позволяет в ряде случаев уменьшить количество команд (например, совмещая пересылку операнда с проверкой его на знак и на нуль). Некоторые команды не изменяют состояния признаков. К таким командам относятся: команды обмена со стеком PSH*, PUL*, команды сложения регистра B с индексными регистрами и команды 16-битовых пересылок и обменов.

Два бита маскирования I,X запрещают реакцию процессора на запросы внешних аппаратных прерываний по входам IRQ и XIRQ соответственно. После сброса по включению питания или по сигналу RESET эти биты установлены в состояние 1 (прерывания запрещены). Для разрешения аппаратных прерываний их надо программно сбросить в нуль. При обработке запроса аппаратного прерывания, после сохранения старого содержимого регистра состояния, биты масок устанавливаются в 1 (т.е. запрещаются вложенные прерывания).

Шина адреса - 16 разрядная. Адресное пространство команд, данных и внешних устройств общее и составляет 64K/ Шина данных - байтовая.

Ширина шины данных и

соответственно регистров данных и АЛУ- 8 бит

Количество регистров данных - 1...2

Ширина адресной шины и соответственно адресных регистров- 16 бит, и

соответственно размер адресного пространства -64K

Количество адресных регистров - 1...2

"Сложные" команды - целочисленное умножение и деление, да и то не

всегда.

Прикладному пограммисту доступны четырнадцать регистров. Их удобно разбить на четыре группы, кратко описанные далее:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.