ГЛАВА 7

КЭШ-ПАМЯТЬ НА КРИСТАЛЛЕ MC68020

В состав микропроцессора MC68020 в качестве средства повышения его производительности включена кэш-память. Она используется для хранения потока команд, считанных в процессе предвыборки из основной памяти.

Исследования показали, что для типичных программ наибольшие затраты времени приходятся на выполнение лишь небольшого числа основных подпрограмм или коротких циклов. Таким образом, активный фрагмент кода, раз оказавшись в высокоскоростной кэш-памяти, может выполняться в режиме выборки команд только из нее.

При этом процессор не испытывает задержек на обращение к внешней памяти и общее время выполнения программы существенно сокращается. Производительность процессора повышена также за счет того, что ему предоставлена возможность одновременной выборки команд из внутренней кэш-памяти и данных из внешней памяти.

Другое важное преимущество использования кэш-памяти состоит в том, что существенно уменьшается загрузка внешней шины процессором. Таким образом, в системе с более чем одним ведущим модулем (такими, как процессор или устройство прямого доступа к памяти) или в сильносвязанной мультипроцессорной системе для конкурирующих модулей доступна большая пропускная способность шины без существенного падения производительности MC68020.

7.1 УСТРОЙСТВО И ФУНКЦИОНИРОВАНИЕ КЭШ-ПАМЯТИ

В следующих разделах описывается устройство и функционирование кэш-памяти в MC68020.

7.1.1 Организация кэш-памяти на кристалле

Кэш-память на кристалле MC68020 является кэш-памятью с прямым отображением и содержит 64 длиннословных элемента. Каждый такой элемент состоит из поля тега (включающего 24 старших бита адреса и значение FC2), одного бита достоверности (V) и 32 бит

(двух слов) команды или ее части.

На Рис.7-1 изображена структурная схема кэш-памяти на кристалле. Всякий раз при выборке команды прежде всего производится проверка наличия требуемого слова в кэш-памяти (если та подключена). Это достигается путем использования индексного поля (A2A7) адреса обращения в качестве индекса в кэш-памяти. Так выбирается один из 64 элементов кэш-памяти. Далее биты A8-A31 адреса обращения и поле FC2 сравниваются с полем тега выбранного элемента. Если отмечено совпадение и бит достоверности установлен, то имеет место попадание в кэш-память. Бит адреса A1 используется для выбора соответствующего слова из элемента кэшпамяти; цикл на этом завершается. Если совпадения нет или сброшен бит достоверности, то имеет место промах мимо кэш-памяти и выборка команды осуществляется из внешней памяти. При этом новая команда автоматически записывается в элемент кэш-памяти и устанавливается бит достоверности, если только в регистре управления кэш-памяти не был установлен бит фиксации кэш-памяти

(см. 7.1.2.3 F - ЗАФИКСИРОВАТЬ КЭШ-ПАМЯТЬ). Поскольку выборку команд извне процессор всегда осуществляет только длинными словами, в элементе кэш-памяти будут обновлены оба слова, независимо от того, какое из них (старшее или младшее) вызвало промах.

Рисунок подлежит сканированию стр. 7-2

Рис.7-1. Организация кэш-памяти на кристалле MC68020

адрес предвыборки

-------T-----------------------------------------------------¬

¦F F F ¦A A A A A A A A A A A A A A A A A A A A A A A A A ¦

¦C C C ¦3 .. 2 2 2 2 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 ¦

¦2 1 0 ¦1 3 2 1 0 9 8 7 6 5 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 ¦

+-T----+-----------------------------------------------------> ¦<- ¦<------------- тег --------------> <

¦ ¦<- индекс->¦ ¦

L---T-------------------- ¦

¦ ----------------------------------------- ¦

¦ ¦ ------------¦ ¦ ¦

¦ ¦ ¦

¦ ¦ выбор v слова

¦ ¦ -----------T----¬ -------T------¬

¦ ¦ ¦ тег ¦ V ¦ ¦слово ¦ слово¦

¦ ¦ +----------+----+ +------+------+

¦ L--> ¦ . ¦ ¦ ¦ . ¦ . ¦

¦ выбор ¦ . ¦ ¦ ¦ . ¦ . ¦

¦ 1 из 64 +----------+----+ +------+------+

¦ ¦ ¦ ¦ ¦ ¦ ¦

¦ L----^-T---+-T--- L-T--^-+T---^-+-- замена ---- ¦ ¦ ¦ L--+---+ замена

¦ тега ¦ ¦ ¦ ¦ данных

¦ ¦ ¦ ¦ ¦--¬

¦ ¦ ¦ L-----++&+->в конвейер

¦ ¦ ¦ LT- команд

¦ ---------v-¬ -+¬ ¦

L------->компаратор+--+&+----попадание-----+-> управление

L----------- L-- кэш-памятью

ЗАМЕЧАНИЕ

Обращения к данным не кэшируются, независимо от кода адресного пространства, из которого те извлекаются.

7.1.2 Управление кэш-памятью

Сама по себе кэш-память доступна только внутреннему устройству управления процессора MC68020. У пользователя нет непосредственной возможности считать/записать отдельный элемент (тег, данные и пр.). Тем не менее, имеется ряд управляющих функций, позволяющих пользователю манипулировать элементами кэш-памяти, манипулируя описываемым ниже регистром управления кэш-памятью.

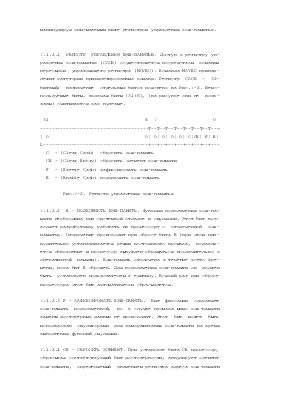

7.1.2.1 РЕГИСТР УПРАВЛЕНИЯ КЭШ-ПАМЯТЬЮ. Доступ к регистру управления кэш-памятью (CACR) осуществляется посредством команды пересылки управляющего регистра (MOVEC). Команда MOVEC принадлежит категории привилегированных команд. Регистр CACR - 32битный; назначение отдельных битов пояснено на Рис.7-2. Неиспользуемые биты, включая биты [31:8], (на рисунке они не показаны) считываются как нулевые.

31 8 7 0

--------------------------------------T--T--T--T--T--T--T--T--¬

¦ 0 0¦ 0¦ 0¦ 0¦ 0¦ C¦CE¦ F¦ E¦

L-------------------------------------+--+--+--+--+--+--+--+--C - (Clear Cash) сбросить кэш-память

CE - (Clear Entry) сбросить элемент кэш-памяти

F - (Freeze Cash) зафиксировать кэш-память

E - (Enable Cash) подключить кэш-память

Рис.7-2. Регистр управления кэш-памятью

7.1.2.2 E - ПОДКЛЮЧИТЬ КЭШ-ПАМЯТЬ. Функция подключения кэш-памяти необходима при системной отладке и эмуляции. Этот бит позволяет разработчику работать на процессоре с отключенной кэшпамятью. Отключение происходит при сбросе бита E (при этом принудительно устанавливается режим постоянного промаха, подавляется обновление и процессор вынужден обращаться исключительно к оперативной памяти). Кэш-память отключена в течение всего времени, пока бит E сброшен. Для подключения кэш-памяти он должен быть установлен пользователем в единицу. Всякий раз при сбросе процессора этот бит автоматически сбрасывается.

7.1.2.3 F - ЗАФИКСИРОВАТЬ КЭШ-ПАМЯТЬ. Бит фиксации сохраняет кэш-память подключенной, но в случае промаха мимо кэш-памяти замены достоверных данных не происходит. Этот бит может быть использован эмуляторами для замораживания кэш-памяти на время выполнения функций эмуляции.

7.1.2.4 CE - СБРОСИТЬ ЭЛЕМЕНТ. При установке бита CE процессор, сбрасывая соответствующий бит достоверности, аннулирует элемент кэш-памяти, определяемый значением регистра адреса кэш-памяти

(CAAR), точнее, значением его поля индекса (биты 2-7). Это происходит вне зависимости от наличия промаха или попадания, иными словами, вне зависимости от того, совпадает ли поле тега в регистре адреса кэш-памяти с полем тега элемента кэш-памяти или нет. Данная функция выполняется только в момент записи в регистр управления кэш-памятью значения, бит CE которого равен единице. Бит CE всегда считывается как нулевой. Результат операции не зависит от состояния битов E, F или значения внешнего сигнала на линии "отключение кэш-памяти" (CDIS*).

7.1.2.5 C - СБРОСИТЬ КЭШ-ПАМЯТЬ. Бит сброса кэш-памяти используется для аннулирования всех элементов кэш-памяти. Эта функция используется операционными системами и иными программными средствами, когда возникает необходимость удаления всех старых данных из кэш-памяти при переключении контекста. Установка бита сброса кэш-памяти в регистре управления кэш-памяти вызывает сброс всех битов достоверности, в результате чего аннулируются все элементы. Данная функция выполняется только в момент записи в регистр управления кэш-памятью значения, бит C которого равен единице. Бит C всегда считывается как нулевой.

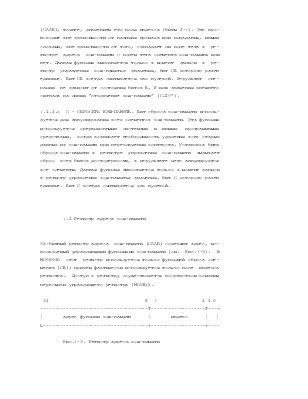

7.2 Регистр адреса кэш-памяти

32-битный регистр адреса кэш-памяти (CAAR) содержит адрес, используемый управляющими функциями кэш-памяти (см. Рис.7-3). В

MC68020 этот регистр используется только функцией сброса элемента (CE); причем фактически используется только поле индекса регистра. Доступ к регистру осуществляется посредством команды пересылки управляющего регистра (MOVEC).

31 8 7 2 1 0

--------------------------------------T-------------------T---¬

¦ адрес функции кэш-памяти ¦ индекс ¦ ¦

L-------------------------------------+-------------------+---Рис.7-3. Регистр адреса кэш-памяти

7.3 Входной сигнал "отключение кэш-памяти"

Входная линия "отключение кэш-памяти" используется для динамического отключения внутренней кэш-памяти. Входной сигнал на этой линии перед использованием синхронизируется. Кэш-память отключается при первом обращении к ней после того, как будет распознана установка синхронизированного сигнала CDIS*. Кэш-память будет заново подключена при первом обращении к ней после того, как будет распознано снятие синхронизированного сигнала

CDIS*. Данная линия отключает кэш-память независимо от состояния бита подключения регистра управления кэш-памятью. Поэтому она может быть использована аппаратурой внешнего эмулятора для того, чтобы вынудить MC68020 выполнять все обращения через внешнюю шину.

7.4 Инициализация кэш-памяти

При сбросе процессора сбрасываются все биты достоверности, в результате чего происходит очистка кэш-памяти. Сбрасываются также биты подключения (E) и фиксации (F) регистра управления кэш-памятью.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.