Основная идея – команда кодирует несколько операций, которые выполняются одновременно на нескольких исполнительных устройствах (конвейерах).

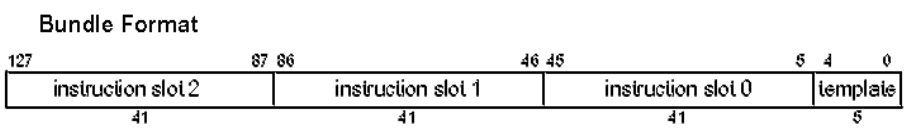

Формат команды IA-64 содержит «связку» (bundle), включающую три 41-битовых поля (slots) инструкций и 5-битовое поле «шаблона» (template):

(Рисунок заимствован из документа 24531902.pdf ‑ Intel® IA-64 Architecture Software Developer’s Manual Volume 3: Instruction Set Reference стр. 265, фиг. 4-1)

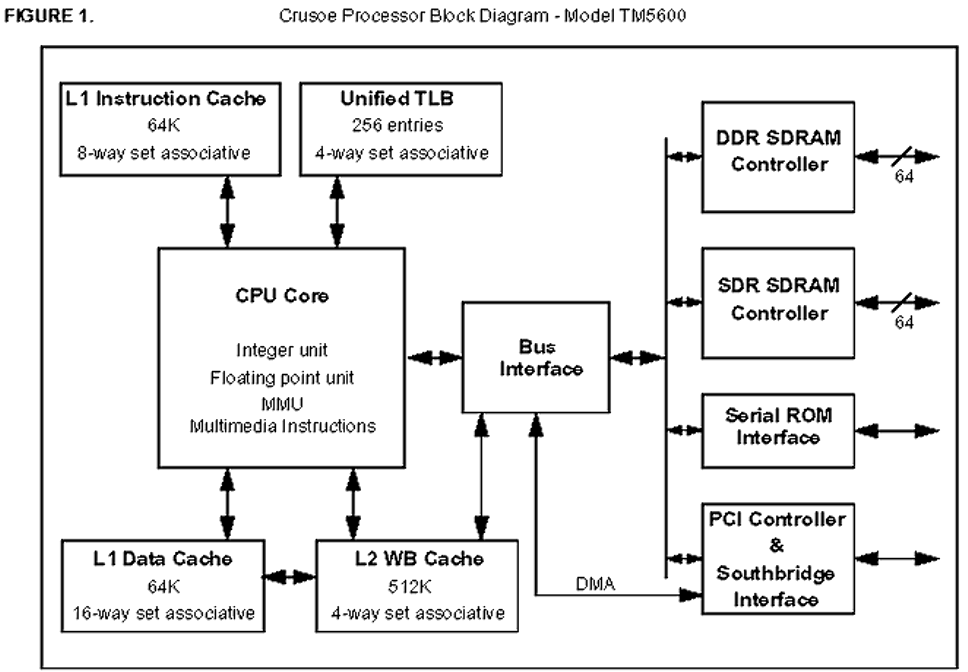

(Рисунок структурной схемы

процессора Crusoe TM5600 заимствован из документа

TM5600_ProductBrief_8-2-00.pdf, стр.2)

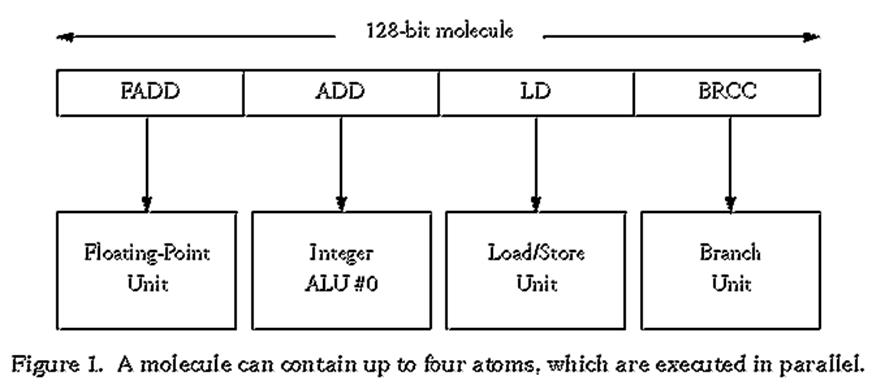

VLIW-команда процессора Crusoe, называемая «молекулой», имеет длину 64 или 128 бит и содержит две или четыре 32-битовых RISC-инструкции, называемые «атомами». Слоты для атомов жестко связаны с исполнительными устройствами, что существенно упрощает схемотехнику декодирования и диспетчирования инструкций.

(Рисунок заимствован из документа crusoetechwp.pdf , стр.4)

Этот процессор описан в книге [8], Корнеев, Киселев, Современные микропроцессоры Стр.217.

За один такт из кэша команд выбирается восемь 32-разрядных команд, каждая из которых содержит условия выполнения, что позволяет избежать команд условных переходов.

Книга [8] Корнеев, Киселев, Стр. 253. Пять АЛУ, связанных 792-разрядной шиной. 72-битовые команды VLIW, содержащие по две SIMD-инструкции длиной 4 или 5 байт.

Лит [8]. В.В.Корнеев, А.В.Киселев. Современные микропроцессоры. – М.: НОЛИДЖ, 2000 г.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.