ГЛАВА 4

ОПИСАНИЕ СИГНАЛЬНЫХ ЛИНИЙ

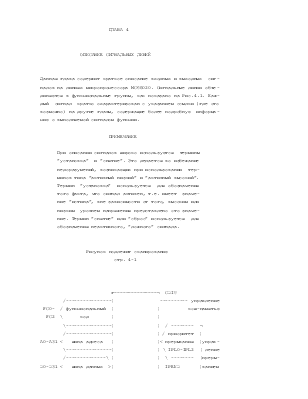

Данная глава содержит краткое описание входных и выходных сигналов на линиях микропроцессора MC68020. Сигнальные линии объединяются в функциональные группы, как показано на Рис.4.1. Каждый сигнал кратко охарактеризован с указанием ссылки (где это возможно) на другие главы, содержащие более подробную информацию о выполняемой сигналом функции.

ПРИМЕЧАНИЕ

При описании сигналов широко используются термины

"установка" и "снятие". Это делается во избежание недоразумений, возникающих при использовании терминов типа "активный низкий" и "активный высокий".

Термин "установка" используется для обозначения того факта, что сигнал активен, т.е. имеет значение "истина", вне зависимости от того, высоким или низким уровнем напряжения представлено это значение. Термин "снятие" или "сброс" используется для обозначения неактивного, "ложного" сигнала.

Рисунок подлежит сканированию стр. 4-1

г===============¬ CDIS

/----------------¦ ---------- управление

FC0- / функциональный ¦ ¦ кэш-памятью

FC2 \ код ¦ ¦

\----------------¦ ¦ / -------- ¬

/----------------¦ ¦ / приоритет ¦

A0-A31 < шина адреса ¦ ¦< прерывания ¦управ\----------------¦ ¦ \ IPL0-IPL2 ¦ ление

/--------------\ ¦ ¦ \ -------- ¦прерыD0-D31 < шина данных >¦ ¦ IPEND ¦ванием

\--------------/ ¦ ¦----------> ¦

SIZ0 ¦ ¦ AVEC ¦

объем - <----------¦ ---------- передачи ¦ SIZ1 ¦ Микро- ¦ BR

L <----------¦ процессор ------- ¬

ECS ¦ ¦ BG ¦ управление

- <----------¦ MC68020 ¦------> ¦ арбитражем

¦ OCS ¦ ¦ BGACK ¦ шины

¦ <----------¦ ------ ¦ RMC ¦ ¦ RESET

¦ <----------¦ ------> ¬ управление

¦ AS ¦ ¦ HALT ¦исключениями управление ¦ <----------¦ ------> ¦ шины

¦ DS ¦ ¦ BERR ¦

асинхронной¦ <----------¦ ------- ¦ R/W ¦ ¦

шиной ¦ <----------¦ ¦

¦ DBEN ¦ ¦ CLK

¦ <----------¦ ---------¦ DSACK0 ¦ ¦ VCC(15)

¦ ---------- ---------¦ DSACK1 ¦ ¦ GND (15)

L ---------- ---------L===============Рис.4-1. Функциональные группы сигнальных линий

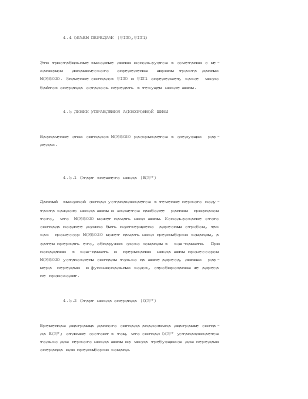

4.1 ЛИНИИ ФУНКЦИОНАЛЬНОГО КОДА (FC0...FC2)

Эти тристабильные выходные линии идентифицируют режим, в котором находится процессор (режим супервизора или пользователя), а также адресное пространство, к которому происходит обращение в выполняемом цикле шины в соответствии с Таблицей 4.1.

Таблица 4-1. Значения функциональных кодов

------T-----T-----T-----------------------------------------¬

¦ FC2 ¦ FC1 ¦ FC0 ¦ тип цикла шины ¦

+-----+-----+-----+-----------------------------------------+

¦ 0 ¦ 0 ¦ 0 ¦ (неопределено, зарезервировано) * ¦

¦ 0 ¦ 0 ¦ 1 ¦ пространство данных пользователя ¦

¦ 0 ¦ 1 ¦ 0 ¦ программное пространство пользователя ¦

¦ 0 ¦ 1 ¦ 1 ¦ (неопределено, зарезервировано) ** ¦

¦ 1 ¦ 0 ¦ 0 ¦ (неопределено, зарезервировано) * ¦

¦ 1 ¦ 0 ¦ 1 ¦ пространство данных супервизора ¦

¦ 1 ¦ 1 ¦ 0 ¦ программное пространство супервизора ¦

¦ 1 ¦ 1 ¦ 1 ¦ пространство ЦП ¦

L-----+-----+-----+-----------------------------------------* зарезервировано фирмой Моторола для будущего использования

** зарезервировано для определения пользователем

Для каждого из значений функционального кода система управления памятью может использовать весь диапазон адресов в 4 гигабайта в соответствующем адресном пространстве.

4.2 ШИНА АДРЕСА (А0...А31)

Эти тристабильные выходные линии используются для задания адреса данных при передаче по шине в случае всех (определенных в действующем ныне стандарте фирмы-изготовителя) циклов шины, за исключением циклов обращения к пространству ЦП. В этом последнем случае шина адреса используется для задания некоторой информации, связанной с работой процессора. Шина адреса позволяет адресовать до 4 гигабайт (2**32) данных.

4.2 ШИНА ДАННЫХ (D0...D31)

Эти тристабильные двунаправленные сигнальные линии образуют универсальный тракт данных между MC68020 и всеми другими устройствами. Данные по шине могут передаваться и приниматься с использованием различной ширины тракта, определяемой процессором MC68020 динамически. Дополнительная информация приведена в следующем разделе.

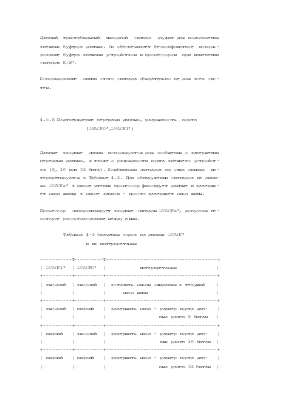

4.4 ОБЪЕМ ПЕРЕДАЧИ (SIZ0,SIZ1)

Эти тристабильные выходные линии используются в сочетании с механизмом динамического определения ширины тракта данных

MC68020. Значение сигналов SIZ0 и SIZ1 определяет, какое число байтов операнда осталось передать в текущем цикле шины.

4.5 ЛИНИИ УПРАВЛЕНИЯ АСИНХРОННОЙ ШИНЫ

Назначение этих сигналов MC68020 раскрывается в следующих разделах.

4.5.1 Старт внешнего цикла (ECS*)

Данный выходной сигнал устанавливается в течение первого полутакта каждого цикла шины и является наиболее ранним признаком того, что MC68020 может начать цикл шины. Использование этого сигнала позднее должно быть подтверждено адресным стробом, так как процессор MC68020 может начать цикл предвыборки команды, а затем прервать его, обнаружив слово команды в кэш-памяти. При попадании в кэш-память и прерывании цикла шины процессором

MC68020 установлены сигналы только на шине адреса, линиях размера передачи и функциональных кодов, стробирования же адреса не происходит.

4.5.2 Старт цикла операнда (OCS*)

Временная диаграмма данного сигнала аналогична диаграмме сигнала ECS*; отличие состоит в том, что сигнал OCS* устанавливается только для первого цикла шины из числа требующихся для передачи операнда или предвыборки команд.

4.5.3 Цикл чтение-модификация-запись (RMC*)

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.