Этот уровень в настоящее время не является ни программно доступным, ни даже наблюдаемым, однако представление о нем помогает пониманию таких вопросов, как скорость выполнения команд, возможность конвейеризации, ...

Выполнение команды уровня Programming Model может быть сведено к нескольким (одновременно, либо последовательно в времени) операциям пересылки из регистра в регистр возможно с промежуточным преобразованием пересылаемых двоичных слов на комбинационных логических схемах.

Посмотрим, как это может быть реализовано.

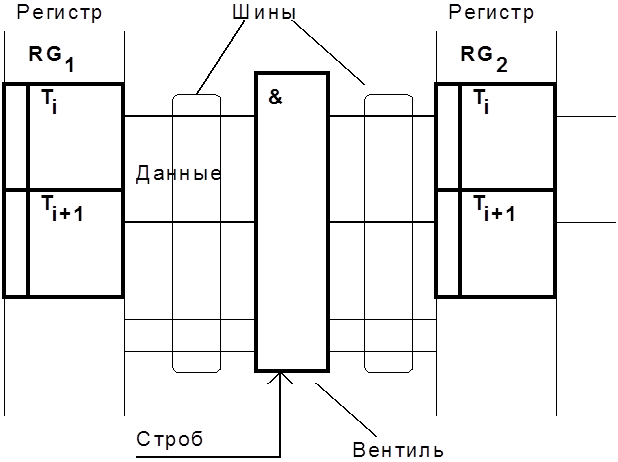

Схема передачи слова данных от источника к приемнику. Она обеспечивает возможность управлять моментом передачи, подавая в нужный момент сигнал "строб".

Хранят двоичное слово. Регистр это линейка триггеров, которые имеют входы для изменения состояния, которое влияет на выходы. Регистры могут быть:

- программно-видимые явно

- видимые косвенно, такие как "теневые" регистры дескрипторов

сегментов

- внутренние для специальных целей, например регистр адреса памяти и регистр

данных для обмена с памятью, про них покрайней мере известно, для чего они...

- внутренние для хранения внутренних промежуточных результатов...

Кроме того, в процессоре могут быть "псевдо-регистры", хранящие константы: 0, 1, -1, и др. (м.б. такие, как p, e,...).

Это просто группа параллельных проводов, связывающих между собой два адресата и позволяющих передать слово данных параллельным кодом.

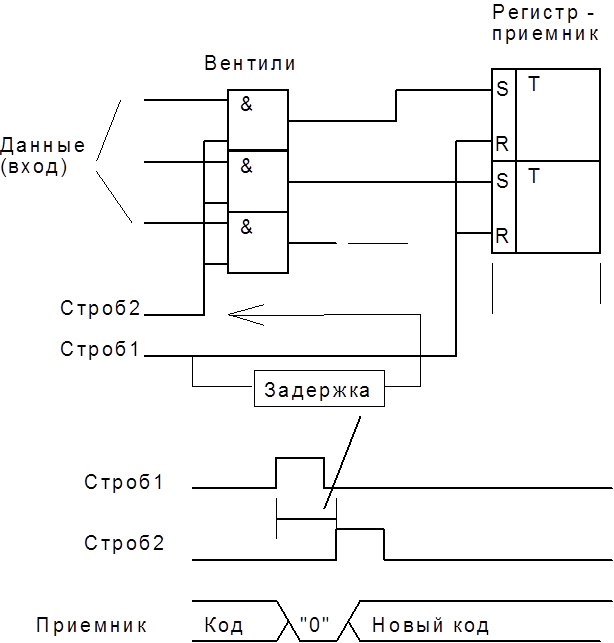

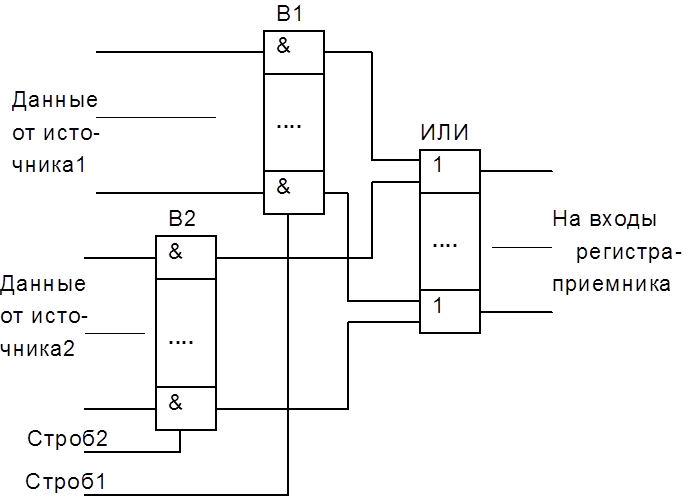

Это логические элементы (коньюнкторы), разрешающие передачу данных (например на вход триггера). Одна из возможных структур вентилей изображена на рисунке. Слово данных от источника данных (им может быть другой регистр) подается на входы элементов "И". Выходы элементов "И" (вентилей) действуют на входы установки регистра-приемника. Для записи нового кода в регистр-приемник надо последовательно выполнить два действия: 1) сбросить старый род в регистре сигналом "Строб1" на его R-входах, 2) разрешить запись сигналом "Строб2" подаваемым на вторые входы вентилей. Можно сформировать сигнал "Строб2" путем задержки сигнала "Строб1".

Если несколько усложнить схему вентиля, то передачу можно осуществить одним стробовым сигналом.

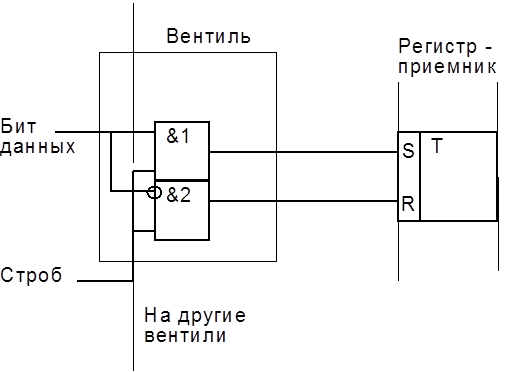

Усложненный вентиль включает два коньюнктора, добавочный элемент &2 своим выходом связан со входом сброса триггера-приемника. При действии строба в зависимости от значения входного сигнала, активный сигнал формируется либо на входе S либо на входе R.

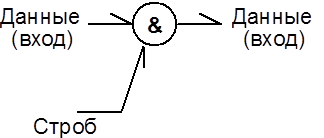

Будем в дальнейшем изображать вентиль схематически следующим образом:

Несколько вентильных линеек В1, В2,...могут быть объединены по выходам линейкой элементов "ИЛИ". Такая структура позволяет передавать слово данных на вход регистра-приемника от одного из нескольких источников при действии разных стробовых сигналов.

Такую структуру принято называть мультиплексором.

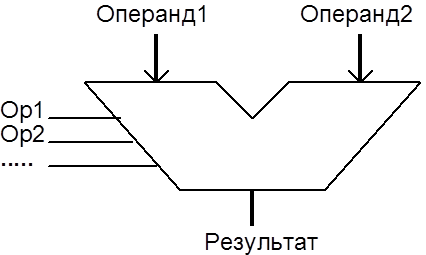

Это комбинационная схема, (т.е. она не

содержит внутри элементов памяти)

- принимающая на два входа два операнда (например содержимые двух регистров) и

- формирующая на выходе результат операции.

Входы и выход АЛУ - чаще всего многоразрядные, т.е. операнды подаются параллельным кодом.

АЛУ обычно способно выполнять несколько различных операций.

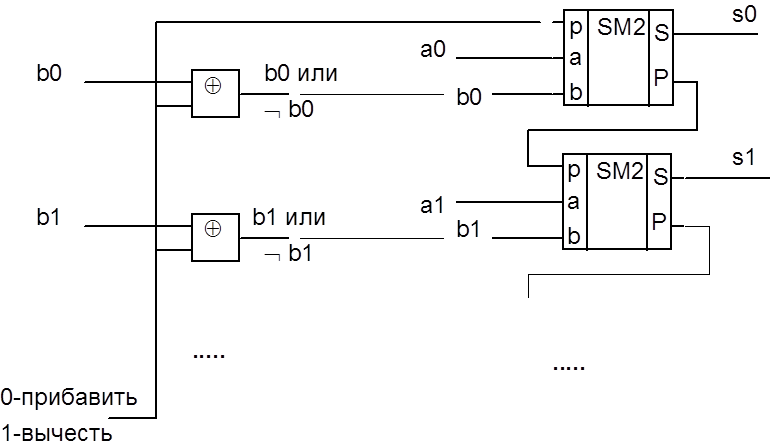

Имею сумматор. Хочу кроме сложения выполнять вычитание. Это можно сделать, заменив вычитание сложением с дополнительным кодом.

a - b = a + bдоп = a + (Øb +1)

Элементы "исключающее или" позволяют выполнять прямую передачу кода, если управляющий сигнал "прибавить/вычесть" равен 0, или инвертирование кода, если управляющий сигнал равен 1. Этот же управляющий сигнал, поступая на вход p младшего разряда сумматора, добавляет 1, необходимую для получения дополнительного кода.

В общем, АЛУ можно представить как комбинационную схему, имеющую две входные шины (туда подаются два операнда) и одну выходную (на ней получается результат). Кроме того, АЛУ имеет несколько управляющих входов, сигналы на которых определяют выполняемую операцию.

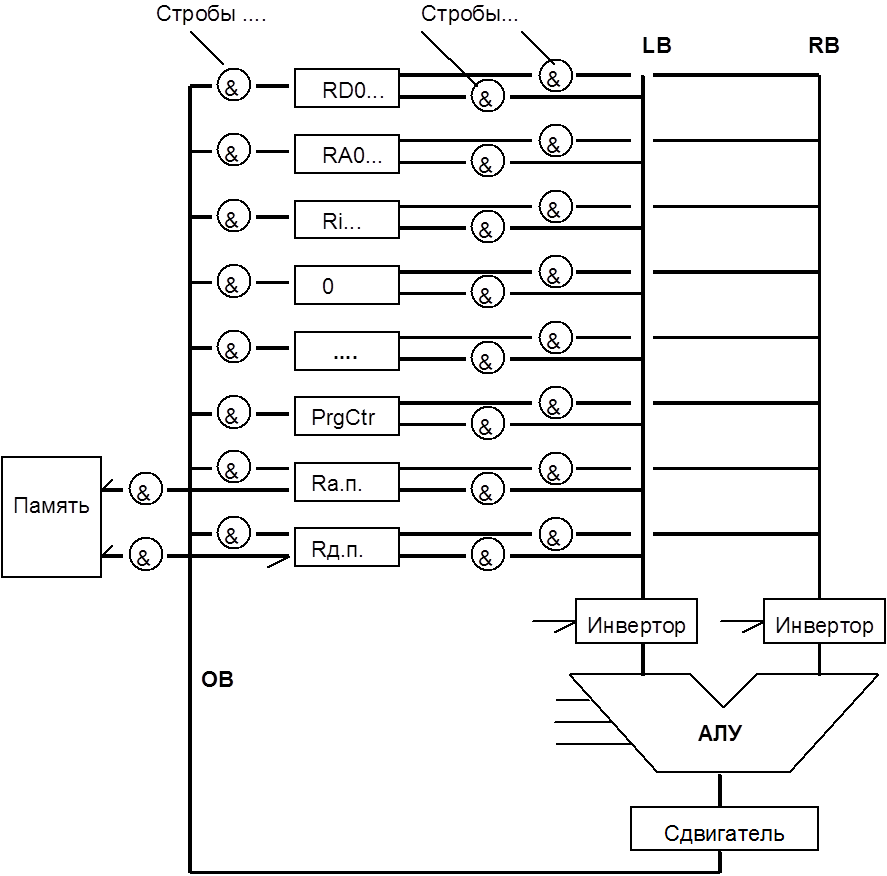

Комбинирование перечисленных узлов позволяет выполнять различные операции.

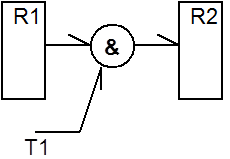

Это действие (этап "испольнение" команды mov R2,R1) реализует структура, изображенная на первом рисунке. Изобразим ее проще:

Для исполнения этого действия достаточно одного стробового сигнала T1.

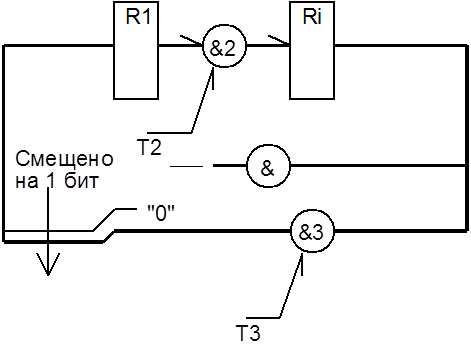

Приведенная схема реализует логический сдвиг влево rol R1. Линии данных с выхода вентиля &3 поданы на вход регистра R1 со смещением в сторону старших разрядов, а на линию младшего разряда подан 0.

Для исключения "гонок" операция проводится за два такта: сначала строб T2 переписывает содержимое регистра R1 во внутренний регистр Ri, а затем строб T3 возвращает операнд в R1 (со смещением на один разряд). Таким образом, исполнение команды "сдвиг" происходит за два такта.

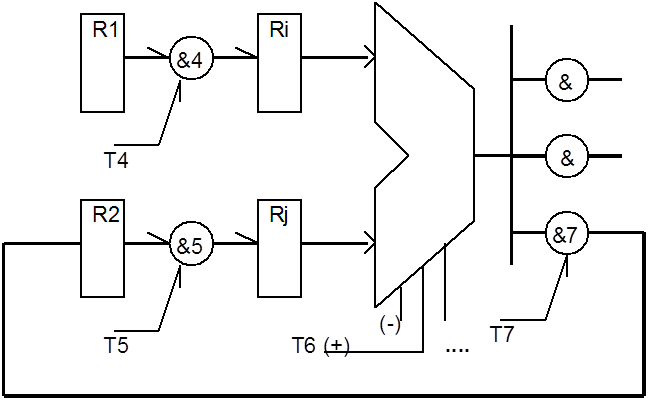

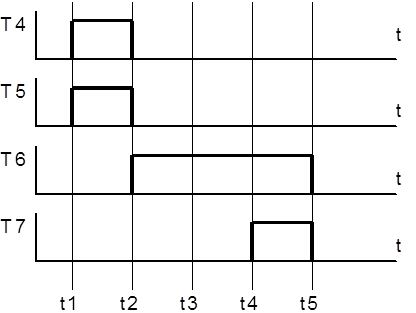

Этап исполнения команды add R2, R1 (приемник в R2 - синтаксис Intel). Содержимое операндов из регистров R1 и R2 надо подать на входы сумматора - это выполняют стробы T4 и T5, подаваемые одновременно. Операнды из регистров R1, R2 передаются во внутренние буферные регистры АЛУ Ri, Rj. На управляющий вход АЛУ после этого надо подать строб T6, разрешающий АЛУ операцию сложения. Через время, не меньшее, чем задержка АЛУ, подается строб T7, разрешающий запись результата с выхода АЛУ в регистр R2.

Временная диаграмма стробов может иметь следующий вид:

В момент t1 подаются стробы T4 и T5, длительность их (t2-t1) должна быть достаточной для надежного переключения триггеров в регистрах Ri, Rj. В момент t2 подается разрешение на АЛУ, время задержки которого (предположим) равно t4-t2. В момент t4 строб T7 переписывает результат сложения с выхода АЛУ в регистр-приемник R2.

Отметим, что каждое из перечисленных действий требует некоторого минимального времени, зависящего от быстродействия логических элементов, причем для разных действий это время, вообще говоря, различно. Система формирования стробов в процессоре основана на дискретной периодической сетке, формируемой тактовым генератором.

Команду машинного уровня можно реализовать, подавая в течение нескольких последовательных тактов стробы на нужные вентили. Как можно сформировать такую последовательность наборов стробов ? Один из способов: использовать ПЗУ, в котором число слов равно числу тактов в команде, а число битов в слове - числу вентилей в процессоре.

Типовая реализация микропрограммного уровня содержит микрокоманды всего двух типов: стробирования GATE и анализа TEST.

|

1 |

0 |

0 |

1 |

1 |

....... |

1 |

1 |

1 |

0 |

0 |

1 |

||||||||||||

|

Биты соответствуют стробам (вентилям) |

Признак GATE |

||||||||||||||||||||||

Микрокоманды считываются из ПЗУ микрокоманд с тактовой частотой, каждый бит команды GATE подается на свой вентиль, и если в считанном бите "единица", то вентиль в данном такте открывается.

|

Адрес |

0/1 |

000...010...000 |

N регистра |

0 |

|

На какой адрес микрокода перейти |

В |

Какой бит проверить на = B (только один бит д.б.=1) |

В каком регистре |

Признак TEST |

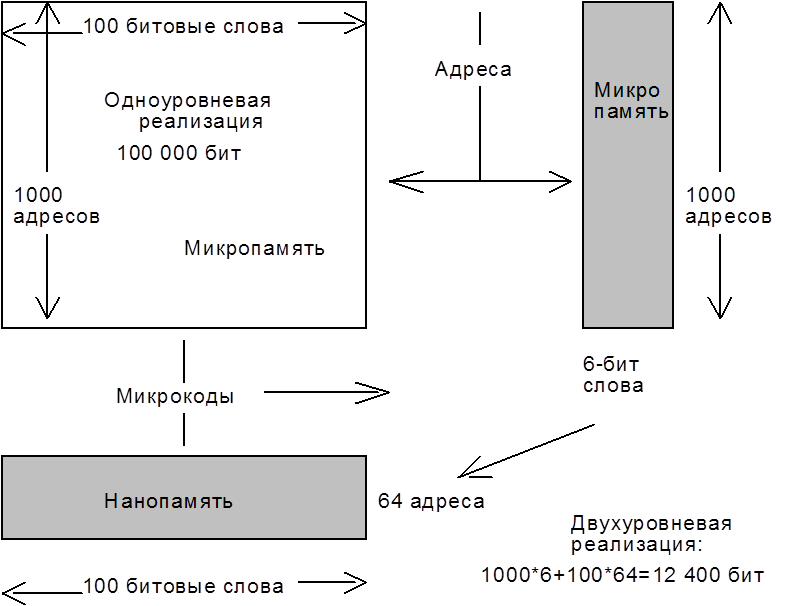

Количество битов в слове д.б. ³ (числа вентилей+1) и в нем должны помещаться все поля микрокоманды TEST. Обычно количество битов в микрокоманде 40...60...100.

Количество микрокоманд должно быть достаточно для кодирования всех команд процессора, обычный объем микрокода 256...1000 слов.

Однако часто оказывается, что количество используемых комбинаций битов (т.е. разных микрокоманд) значительно меньше количества слов в микрокоде. Тогда можно расщепить микропрограммный уровень на два.

Приведем пример "аппаратной и микропрограммной" реализации.

Пусть надо реализовать этап исполнения команды sub R1, R0 ; R1-R0 -> R1

Если АЛУ умеет выполнять вычитание, тогда процесс исполнения может быть таким:

1) R0 -> LB и r1 -> RB //

Помещаем операнды на входы АЛУ

2) АЛУ - вычитание // Делаем вычитание

3) Выход АЛУ -> R1 // Записываем результат

Если же АЛУ не умеет делать вычитание, а только складывает, тогда делаем так:

1) R0 -> LB и Инв.LB и -1 ->

RB

2) АЛУ - сложение // Получаем доп. код R0

3) Выход АЛУ - > Ri // и сохраняем его во временном

регистре

4) Ri -> LB и R1 -> RB //

5) АЛУ - сложение // Складываем с доп. кодом

6) Выход АЛУ - > R1 // Записываем результат

См. конкретный пример внутренней структуры, аналогичной рассмотренной – структура вычислительного ядра микроконтроллера MCS51 – стр.2 документа по ссылке.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.