Оглавление

1. Техническое задание . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

2. Анализ технического задания . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

3. Описание принципиальной схемы . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

4. Расчет константы пересчета . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

5. Программа . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

6. Алгоритм работы системы. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

7. Список использованных источников. . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Список приложений:

Приложение A Схема электрическая принципиальная

Приложение B Схема структурная

Приложение B Перечень элементов

1. Техническое задание

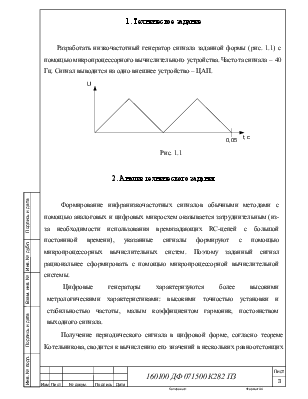

Разработать низкочастотный генератор сигнала заданной формы (рис. 1.1) с помощью микропроцессорного вычислительного устройства. Частота сигнала – 40 Гц. Сигнал выводится на одно внешнее устройство – ЦАП.

Рис. 1.1

2. Анализ технического задания

Формирование инфранизкочастотных сигналов обычными методами с помощью аналоговых и цифровых микросхем оказывается затруднительным (из-за необходимости использования времязадающих RC-цепей с большой постоянной времени), указанные сигналы формируют с помощью микропроцессорных вычислительных систем. Поэтому заданный сигнал рациональнее сформировать с помощью микропроцессорной вычислительной системы.

Цифровые генераторы характеризуются более высокими метрологическими характеристиками: высокими точностью установки и стабильностью частоты, малым коэффициентом гармоник, постоянством выходного сигнала.

Получение

периодического сигнала в цифровой форме, согласно теореме Котельникова,

сводится к вычислению его значений в нескольких равноотстоящих точках периода с

определённым шагом дискретизации ![]() и циклическому повторению этих

вычислений.

и циклическому повторению этих

вычислений.

Работа цифрового генератора основана на принципе формирования числового кода с последующим преобразованием его в аналоговый сигнал, который аппроксимируется функцией, моделируемой с помощью ЦАП. Разрабатываемая микропроцессорная система может выводить либо уже готовые значения отсчетов, записанные в память, либо производить отдельные вычисления уже в процессе работы.

Рациональнее производить отдельные вычисления для каждой точки, т.к. аналитическое выражение заданного сигнала является простым, и расчет не займет много времени. Время формирования одного отсчета микропроцессорной системой в этом случае складывается из времени расчета значения и времени вывода.

Первую половину периода сигнал линейно нарастает, что соответствует операции сложения (для получения нового отсчета к предыдущему значению добавляется некоторая величина), далее сигнал опять же линейно уменьшается до нуля.

Ограничим разрядность выходного кода 8-ю разрядами, тогда максимальное значение напряжения, формируемого ЦАПом, будет соответствовать значению кода 255.

Для удобства расчётов примем, что максимальное значение выходного кода равно 250.

Тогда, если принять, что каждый последующий отсчёт, выводимый на ЦАП, отличается от предыдущего на единицу, всего за период сигнала имеет смысл вывести 500 отчётов (за первую половину периода выводимый код нарастает от 0 до 250, затем уменьшается опять до нуля).

Частота дискретизации в этом случае составит:

![]() . 2.1

. 2.1

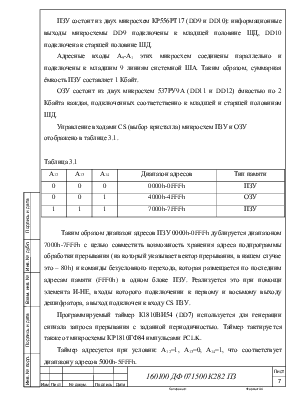

Для построения управляющей системы будет использован центральный процессор КР1810ВМ86 (DD2), имеющий 16-разрядную шину данных,

20-разрядную шину адреса. ЦП выполнен по n-МОП-технологии и электрически совместим с микросхемами ТТЛ и ТТЛШ.

Для хранения исполняемой программы необходимо ПЗУ (DD9, DD10), а т.к. схема предполагает работу с прерываниями, для формирования стека необходимо ОЗУ (DD11, DD12).

Для генерирования периодического сигнала, определяющего шаг дискретизации

![]() можно использовать программируемый

таймер К1810ВИ54 (DD7), имеющийся в микропроцессорном

комплекте К1810.

можно использовать программируемый

таймер К1810ВИ54 (DD7), имеющийся в микропроцессорном

комплекте К1810.

Для преобразования сигнала в аналоговую форму можно применить стандартную схему, состоящую из буферного регистра KР580ИР82 (DD14) и ЦАП К1108ПА2 (DD15). Преобразование выходного тока в напряжение реализуем на операционном усилителе (DA1).

3. Описание принципиальной схемы

Поскольку система имеет сравнительно небольшое число ИС, микропроцессор работает в минимальном режиме.

Стандартным

образом к микропроцессору подключается генератор тактовых импульсов К1810ГФ84 (DD1). ГТИ работает в режиме формирования сигналов от внешнего

генератора, частота которого задается с помощью кварцевого резонатора частотой ![]() , который подключается к выводам Х1 и

Х2. Внутренний делитель частоты формирует синхронные выходные импульсы CLK и PCLK, частоты которых

определяются соотношением 3.1.

, который подключается к выводам Х1 и

Х2. Внутренний делитель частоты формирует синхронные выходные импульсы CLK и PCLK, частоты которых

определяются соотношением 3.1.

![]() (3.1)

(3.1)

![]() – тактовая частота для ЦП.

– тактовая частота для ЦП. ![]() – тактовая частота для управления устройствами,

работающими на ТТЛ-уровнях.

– тактовая частота для управления устройствами,

работающими на ТТЛ-уровнях.

ГТИ также формирует выходной сигнал RESET (сброс), инициализирующий систему, при поступлении сигнала на вывод RES, к которому подключена RC-цепочка, которая формирует сигнал сброса автоматически при включении питания либо с помощью кнопки SA1.

Задача демультиплексирования шины адреса/данных решается с помощью буферных регистров К580ИР82 (DD3 и DD4) и двунаправленных шинных формирователей К580ВА86 (DD5, DD6).

Дешифрация адресов в проектируемом устройстве происходит по принципу совмещёной адресации, т.е. адресное пространство ввода/вывода не отделено от адресного пространства памяти.

При подключении запоминающих устройств к шинам микропроцессорной системы необходимо обеспечивать передачу как двухбайтовых слов, так и отдельных байтов.

С этой целью память выполняется в виде двух банков: младшего, подключаемого к линиям данных D7-D0 и содержащего байты с чётными адресами (А0=0), и старшего, соединённого с D15-D8 и содержащего байты с нечётными адресами (А0=1).

Адресная линия А0 совместно с линией разрешения старшего банка BHE обеспечивает следующие варианты пересылок по шине данных:

А0=0; BHE=0 – пересылается слово;

А0=0; BHE=1 – пересылается только младший байт;

А0=1; BHE=0 – пересылается только старший байт;

Выработка сигнала BHE и указанный порядок пересылок реализуются микропроцессором автоматически при выполнении команды.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.