Содержание:

1. Техническое задание...................................................... 2

2. Анализ технического задания...................................... 2

3. Алгоритм работы системы............................................. 3

4. Инициализация адресного пространства................... 4

5. Описание принципиальной схемы............................... 4

6. Программа......................................................................... 5

7. Расчёт частоты дискретизации..................................... 7

8. Список литературы.......................................................... 7

9. Перечень элементов......................................................... 8

Разработать низкочастотный генератор сигнала заданной формы (рис.1) с помощью микропроцессорного вычислительного устройства.

|

![]()

0,75Т

Рис.1 Форма генерируемого сигнала.

Частота сигнала – 50 Гц. Сигнал выводится на одно внешнее устройство – ЦАП.

Идея проектируемого устройства заключается в том, что микропроцессорное вычислительное устройство выводит на цифро-аналоговый преобразователь с определенной частотой отсчеты низкочастотного сигнала, который обычными методами (с использованием времязадающих RC-цепей) получить затруднительно.

При этом МП может выводить либо уже готовые значения отсчетов, записанные в память, либо для каждой точки производить отдельные вычисления уже в процессе работы.

Очевидно, что аналитическое выражение заданного сигнала является простым, поэтому вычисление отсчетов по ходу работы не займет много времени, т.е. выгоднее каждый раз считать значения отсчетов, чем ставить ПЗУ большой емкости, содержащее уже вычисленные отсчёты (разводка, питание и т.д). Время формирования одного отсчета микропроцессорной системой в этом случае складывается из времени расчета значения и времени вывода и будет рассчитано ниже.

Первые три четверти периода сигнал линейно нарастает, что соответствует операции сложения (для получения нового отсчета к предыдущему значению добавляется некоторая величина), далее сигнал опять же линейно уменьшается до нуля.

Проектируемое устройство по возможности будем выполнять на микросхемах, выполненных по технологии ТТЛ и ТТЛШ или совместимыми с ними по быстродействию, нагрузочной способности и т.д.

Микросхемы ТТЛ и ТТЛШ отличаются хорошими электрическими параметрами, удобны в применении, могут иметь высокий уровень интеграции и обладают большим функциональным разнообразием, что обусловило их широкое распространение в современной цифровой аппаратуре.

Ограничим разрядность выходного цифрового кода 8-ю битами, тогда для построения микропроцессорной системы можно использовать ЦПУ КР1810ВМ88, имеющее 8-разрядную шину данных, выполненное по n-МОП-технологии и электрически совместимое с микросхемами ТТЛ и ТТЛШ.

Базовая МПС включает в себя модуль МП, тактовый генератор, ОЗУ и ПЗУ.

Исходя из требований технического задания можно заключить, что проектируемое устройство не нуждается в специальных микросхемах оперативной памяти, т.к. количество используемых переменных (текущий отсчет сигнала, счетчик отсчетов и т.д.) невелико и вполне может уместиться в блоке РОНов микропроцессора.

ПЗУ необходимо для хранения программы.

Модуль микропроцессора включает в себя буферный регистр для защелкивания адреса, двунаправленный формирователь шины данных и схемы формирования сигналов управления внешними устройствами.

Счёт временного интервала между двумя последовательными отсчётами можно осуществить с помощью программируемого таймера, который будет формировать сигнал “запрос прерывания” на микропроцессор с требуемой периодичностью.

Для хранения дополнительной информации, связанной с обработкой запроса прерывания необходимы ещё две микросхемы: ПЗУ на 4 байта, содержащее адрес подпрограммы обработки прерывания и однобайтовый регистр, содержащий номер используемого вектора прерывания.

Для преобразования сигнала в аналоговую форму можно применить стандартную схему, состоящую из буферного регистра, ЦАП и операционного усилителя.

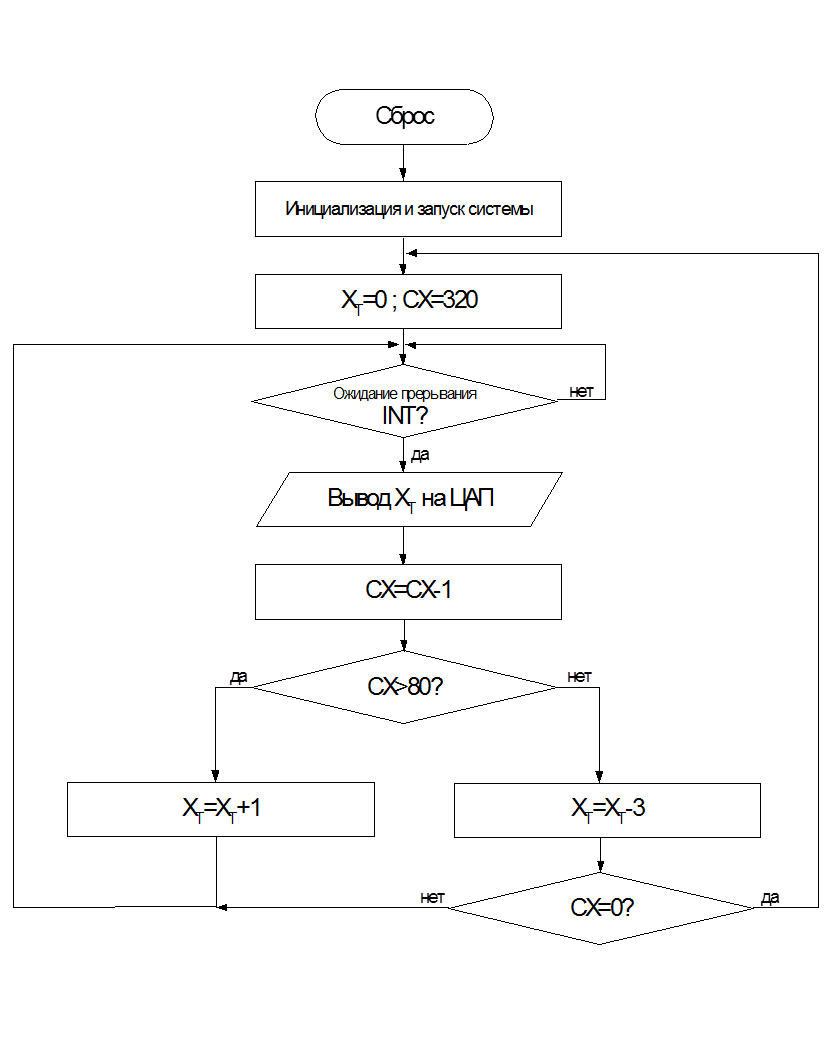

Рис.2 Блок-схема алгоритма работы системы.

Примечания: ХТ – текущий отсчет сигнала; переменная CX содержит информацию о номере текущего отсчета (счетчик времени);

Проектируемое устройство содержит 4 периферийных устройства, управление которыми осуществляется по адресным линиям: ПЗУ программы (512 байт), ПЗУ таблицы прерываний (4 байта), таймер и регистр-защёлка перед ЦАП.

Сигналы управления указанными устройствами формируются на основе сигналов на адресных линиях и состояния вывода M/IO с помощью обычных комбинационных логических схем следующим образом:

|

M/IO |

A10 |

A9 |

A3 |

A2 |

Адресуемая микросхема |

Диапазон адресов |

|

1 |

0 |

0 |

-- |

-- |

ПЗУ таблицы прерываний |

0000h÷0003h |

|

1 |

1 |

1 |

-- |

-- |

ПЗУ программы |

600h÷7FFh |

|

0 |

-- |

-- |

0 |

1 |

Таймер |

04h÷07h |

|

0 |

-- |

-- |

1 |

0 |

Регистр перед ЦАП |

08h |

Табл.1 Распределение периферийных устройств по адресным линиям

Таким образом, адресное пространство системы организовано по принципу раздельной адресации, т.е. адресное пространство ввода-вывода отделено от памяти и обращение к памяти или ВУ зависит от состояния вывода M/IO.

В цикле обращения к памяти (M/IO=“1”) младшие 9 разрядов ША служат для адресации одного из байтов в ПЗУ, в цикле обращения к ВУ для этой цели используются только 2 младших разряда ША.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.