15. Распределители.

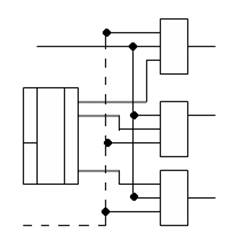

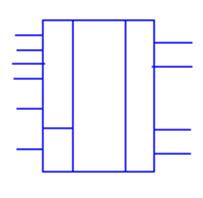

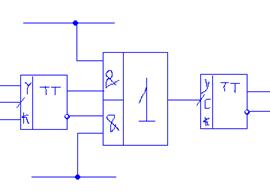

Это устройство, предающее импульс поступивший на его информационный вход, на один из его выходов, в зависимости от управляющего сигнала заданного двоичным кодом. Распределитель может быть выполнен на основе дешифратора:

Уравнивающий сигнал yС в виде парал-го двоичного кода подается на вход дешифратора, выходы к-го соед-ны со средними входами коньюнктеров выходной части схемы. На входах C,EN поддержив. логич. 1. Такой распределитель может быть выполнен синхронным. Для этого используются входы дешифратора C и EN либо третьи входы коньюнктеров, на которые может быть подан сигнал синхронизации Cn.

16. Мультиплексоры.

Представляет собой устрой-во

подключ-ее свой единственный выход к одному из информационных входов, номер

к-го задается двоичным кодом, поступившем на управляющ входы. Мультиплексор

позволяет производить прием сигналов, поступающих с различных направлений, т.е.

мультипл. решает задачу обратную распределителю. Между числом информац. входов n и числом

адресных входов m должно выполнятся соотношение: n![]() 2m

2m

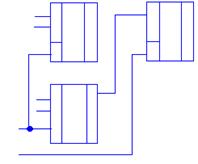

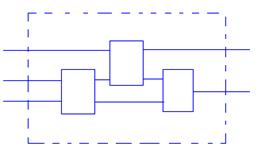

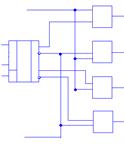

Каскадное соединение MS.

17. Демультиплексоры.

Это устрой-во, в к-м сигналы с одного информационного входа поступают в требуемой последовательности на нужный выход в зависимости от двоичного кода на адресных шинах.

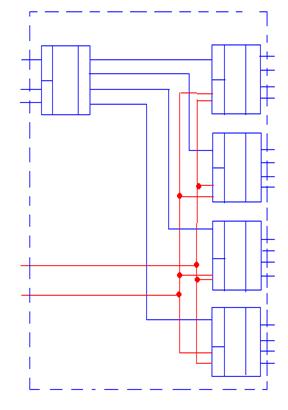

Каскадное включение DMS.

18. Цифровые компараторы (схемы сравнения).

Эти устройства выполняют сравнение 2-х чисел заданных в двоичном коде. Эти устройства широко используются как автономно, так и в составе более сложных схем, например, в сумматорах.

В микросхеме компараторов имеются расширенные коды, к-е позволяют наращивать разрядность сравниваемых чисел путем каскадного и парал-го соединений.

|

входы |

выход |

|

Ai Bi |

yi |

|

0 0 |

1 |

|

0 1 |

0 |

|

1 0 |

0 |

|

1 1 |

1 |

19. Комбинационные сумматоры. Структурная схема одноразрядного сумматора.

Принцип построения сумматора вытекает из правил сложения двоичных цифр. Все многообразие операций можно свести к единственной операции сложения прямых и обратных входов чисел, сдвинутых влево и вправо на определ. число разрядов, поэтому один из основных узлов ЦВМ яв-ся сумматор.

|

ai |

bi |

Si |

Pi |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

20. Принцип построения сумматора многоразрядных двоичных чисел и их виды.

При суммировании двоичных многоразр. чисел для каждого разряда, кроме младшего, необходимо использовать схему, имеющую дополнит. вход-перенос. Такое устр-во яв-ся полным сумматором, можно предст-ть, как объединение 2-х полусумматоров.

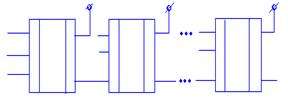

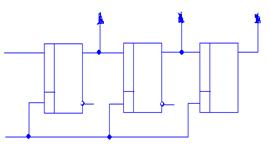

n-й сумматор с послед. переносом:

Различают последоват. и парал. сумматоры.

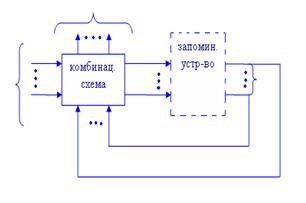

21. Последовательностные автоматы.

В них выходные сигналы в каждый данный момент времени зависит не только от значений входных сигналов в этот же момент времени, но и от значений входных сигналов в предшедст. момент врем.

Если автомат может находиться в нескольких состояниях, то его реакция на входных сигналах опред-ся не только этим входным сигналом, но и текущим состоянием автомата.

Понятие состояние автомата предполагает наличие у него внутр. памяти, где должна храниться инф-ция от предыд. воздействий. В комбинац. схемах вх. и вых. сигналы связаны логич. ф-ми, вида:

![]()

В послед. устр. значение вход. перем. Y(n)(t) на n-м такте работы опред. не только текущим значением X, но и внутр. сост. Сn(t), этого устр-ва. Т.к. Сn(t) зависит от вход. сигн., то аналитич. работу послед. автомата можно охарак-ть в след. систему:

![]()

22. Понятие об автоматах Мура и Мили, их отличие.

![]() Автомат Мура

описывается след. ф-ми: C(n)(t)=f(C(n-1)(t),X(n-1)(t))

Автомат Мура

описывается след. ф-ми: C(n)(t)=f(C(n-1)(t),X(n-1)(t))

Y(n)(t)=φ(C(n)(t))

Т.е каждое новое соотнош. в этом автомате обусловлено и предшест. сост., и вход. сигн.; а выход в каждый момент времени однозначно опред-ся сост. автомата в этот момент времени. Выходными сост. автомата Мура яв-ся внутр. сост., т.е сигналы с выхода устр-ва памяти. Примером таких автоматов яв-ся триггеры, счетчики, накапливающие сумматоры, регистры и т.д.

Автоматы Мили отличаются от автоматов Мура тем, что выход зависит не только от текущего состояния, но и от входного сигнала. Кроме аналитич. записи ф-ции состояний и выходов могут подаваться в виде таблиц. Если ф-ции переходов и выходов заданы на всем множестве комбинаций аргументов X и C, то такие автоматы полностью определенные.

Автоматы Мура и Мили можно описывать с помощью направлен. графов.

Вершины графа соот-т сост. автомата, а дуги перехода однозначно отражают таблицу перехода.

23. Триггеры: опред-е, виды и классификация.

Простейшие конечные цифровые автоматы, обладающими памятью, называют триггерами. Они способны хранить один разряд двоич. чисел, т.е 1 бит инф-ции. Триггер, как конеч. автомат хар-ся след. св-ми: 1) Возможное число внутр. сост. равно 2 2) Число выход. перем. y=1, 3) Число вход. переем. x зависит от типа триггера.

Выход триггера, с к-го в исходном сост. снимается высокий потенциал наз-ся прямым; низкого уровня - инверсным.

По функц-м возмож-тям различ-т:

а) триггеры с раздельным запуском;

б) триггеры задержки;

в) триггеры со считанным входом;

г) универсал. триггеры.

По способу записи инф-ции триггеры подразд-ся на асинхронные и синхронные(тактируемые)

24. Регистры: назначение и классификация.

Регистр представляет собой узел, предназнач. для приема, врем. хранения и выдачи n-разрядного машинного слова. Регистры образуются из упорядоч послед-ти триггеров, число к-х соотв-т числу разрядов в машинном слове. С каждым регистром обычно связано комбинац. цифровое устр-во, с помощью к-го обеспеч-ся выполнение некоторых операций над словами, а именно – прием слова в регистр, выдача слова из регистра, поразрядные логич. операции, сдвиг слова влево и вправо на заданное число разрядов, преобр-ние послед-го кода слова в парал-ный и обратно, установка регистра в начал. сост.

Классификация:

Регистры:

1) накопительные

2) сдвигающие:

а) последоват. ввод-вывод

-параллельные

-последовательные

-комбинационные

б) направ. передачи

-однонаправленные

-реверсивные

25. Функциональная схема n-разрядного регистра, виды и особенности работы.

УГО RG

![]()

![]()

Схема:

Схема регистра, дополненная логич. эл-ми для преобразования хранящ. в регистре кода, позволяет по сигналу «прямой код» считывать пр. код хранящихся данных, а по сиг. «обрат. код» позвол. считывать инверсное значение каждого разряда слова.

Виды:

Из парал-х регистров или регистров памяти составляют регистры файлов, т.е блоки регистровой памяти. Такие блоки позволяют хранить несколько слов с возмож-тью независимой и одновременной записью одного слова и считанного другого.

Среди интеграл. схем в библиотеке БИС и СБИС имеется много различных вариантов регистров, в том числе универсал. и многофункционал. В частности имеющие разнотипные вход и выход играют важную роль для сотовых технологий. Поскольку передача цифровой информации в сетях произв-ся в последовательных кодах, а её обработка в процессорах ЭВМ в парал-х кодах.

26. Счетчики: назначение и характеристики, классификация.

Счетчиком наз-ся узел ЭВМ, позволяющий осуществлять подсчет поступающих на его вход сигналов и фиксацию полученного результата в виде многоразрядного двоичного кода.

Счетчики представляют собой конечные автоматы, внутр. сост. к-х опред-ся только кол-вом логич. единиц.

Счетчики строятся на базе элементах конечных автоматов, к-ми яв-ся триггеры. Кол-во триггеров необходимых для реализации соответ-го счетчика можно выразить ф-лой: m>log2kcr.

Соответ-но счетчик имеющий n- триггеров или разрядов позволяет рассчитывать число сигналов: N=2m.

Счетчики могут быть асинхрон. и синхрон.

Счетчики принято классифицировать по следующим признакам:

1) По модулю счета:

- двоич.-десятич.

- двоич.

- с произвольн. пост. модулем счета

- с переменным модулем счета

2) По направлению счета:

- суммирующие

- вычитающие

- реверсивные

3) По способу формирования внутр. связей:

- с последоват. переносом

- с парал-м переносом

- с комбиниров. переносом

- кольцевые

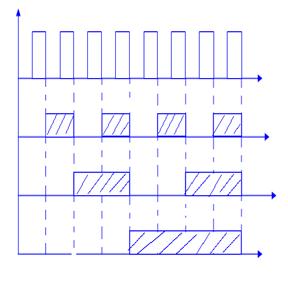

27. Схема суммирующего 3-х разрядного счетчика, таблица истинности и временные диаграммы его работы.

Таблица истинности:

|

№ |

Состояние выходов |

||

|

Q1 |

Q2 |

Q3 |

|

|

0 1 2 3 4 5 6 7 8 |

0 0 0 0 1 1 1 1 0 |

0 0 1 1 0 0 1 1 0 |

0 1 0 1 0 1 0 1 0 |

Временная диаграмма:

28. Вычитающие и реверсивные счетчики.

Если в схеме суммир. 3-х разрядного счетчика использовать не прямые, а инверсные выходы, то получают не суммирующий, а вычитающий счетчик. При этом в исходном состоянии в счетчик должно быть записано максимальное двоичное число, тогда с приходом каждого поступающего импульса содержимое счетчика будет уменьшаться на 1.

чтобы сделать счетчик реверсивным, необходимо обеспечить подачу на входы триггеров сигналы либо с прямых, либо с инверсных выходов.

29.Суммирующие устройства, структура и принцип действия.

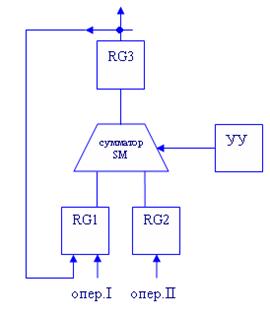

Сумматор – это узел ЭВМ, в к-м происходит суммирование кодов чисел.

Обычно любой сумматор предст-т комбинацию одноразрядных сумматоров.

По принципу построения различают накапливающие и комбинационные сумматоры.

Сумматоры накаплив. типов строятся на I,K, R, C триггера, заполняя их выходы достаточно сложными схемами формирования и распространения переноса.

Из-за того, что процесс сложения в них осущ-ся поэтапно, и прцесс формирования окончат. рез-та может требовать дополнит. тактовых интерваловю

Многоразрядные схемы сумматоров использ-ся редко.

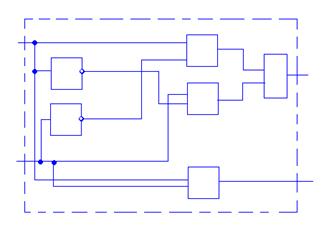

У комбинацион. сумматоров на входе обычно имеются регистры для хранения и преобр. кодов операндов и результата.

Регистор RG1 предназначен для хранения кода I операнда, RG2-для II операнда.

Сумматор (SM) по сигналам из устройств управления выполняет операцию в соотв-ии с кодом этой операции, рез-т опред-ся в регистр RG3, при необходимости этот рез-т может использ-ся для продолжения вычислений.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.