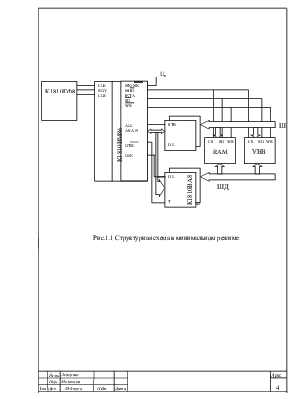

программируемый контроллер прерываний, БД - буфер шины данных, ДА - дешифратор адреса).

3. Распределение памяти и задание адресных портов

Память в ЭВМ на базе К1810ВМ86 организуется как одномерный массив байтов, каждый из которых имеет свой 20-разрядный физический адрес(00000-FFFFF).

Порядок размещения данных в памяти обычный: слово занимает 2 соседние ячейки памяти, причем первым идет младший байт слова, а вторым старший. Физическим адресом слова считается адрес младшего байта слова.

20-ти битный физический адрес ячейки памяти содержится в объекте: сегмент + смещение. Причем на сегмент и на смещение отводится по 2 байта. Следовательно полный физический адрес размещается в 4-х ячейках памяти.

![]() 00002 смещение

00002 смещение

![]() 00003

00003

00004 сегмент

00005

Физическим адресом этого модуля считается адрес младшего байта смещения.

Все пространство памяти объемом 1М разбито на сегменты по 64 К (16 сегментов). Каждому сегменту программой задается его начальный адрес который заносится в сегментные регистры (CS,SS,DS,ES).Такая организация вычислений 20-ти разрядного фактического адреса обусловлена тем, что МП является 16-ти разрядным и все вычислительные операции должны выполняться словами.

Механизм вычисления фактического адреса следующий: содержимое сегментного регистра сдвигается на 4 бита влево. К содержимому смещения присваивается 4 нуля слева.

При суммировании может возникать перенос из разряда A19 в A20. Этот перенос игнорируется. Аналогичную кольцевую организацию имеет каждый сегмент. При выборке команда: CS +IP = ФА команды. При обращении к стеку: SS +SP =ФА стека.

Обращение к данным может производиться из любого сегментного регистра: DS (SS,CS,ES) +EA = ФА данных. EA – эффективный адрес, константа, указанная в программе.

К данным можно обратиться через индексные регистры SI и DI; причем индексный регистр хранит смещение на адрес ячейки памяти, откуда данные можно извлечь. А DI хранит смещение на адрес ячейки памяти, куда данные можно направить: DS(SS,CS,ES) +SI=ФА данных; ES+DI =ФА данных. Обращение через регистр BX: ES(CS,SS,DS)+BX= ФА данных. Такая модульная организация памяти посегментно позволяет писать программы в виде отдельных модулей.

Дешифратор адреса должен обеспечивать формирование сигналов выбора ПЗУ, клавиатуры и индикации при обращении к ним. В связи с неполным использованием адресного пространства в MК клавиатура и индикация входят в адресное пространство МП. При этом для обращения к клавиатуре и индикации будут использованы такие же команды обращения как команды обращения к ячейкам памяти.

Память один из основных элементов устройства, она организована как множество ячеек, в которых может храниться информация. Совокупность всех ячеек памяти, к которым может обратиться МП, составляет адресное пространство памяти. Информационная емкость одной ячейки составляет 8 бит или 1 байт. В каждом из последовательно расположенных байтов имеется свой порядковый номер, называющийся адресом. Если необходимо запомнить значение больше 1 байта, то оно занимает несколько последовательно расположенных ячеек памяти. Любые два смежных байта образуют 16-битовое слово, младшая часть слова имеет меньший адрес, а старший байт - больший адрес.

Наибольший объем памяти, который может быть использован в устройстве, определяется объемом адресного пространства. Блоки памяти, составляющие адресное пространство, распределены по системе и имеют конкретное назначение.

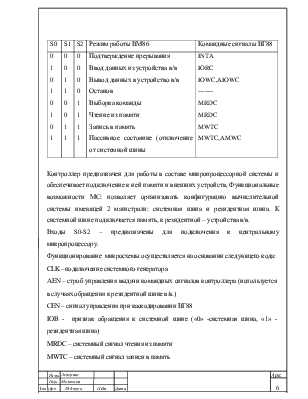

Важным этапом конструирования микроконтроллера является организация памяти, и поэтому при разработке программного обеспечения важно внимательно провести распределение памяти. Область памяти в данном проекте распределена с использованием разрядов адреса А15, А14, А13 при подаче их на адресные входы дешифратора. Таблицы 6.1 и 6.2 поясняют работу ДША в зависимости от значений разрядов адреса

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.