На транзисторах VT1, VТ2 и VТЗ выполнен токовый переключатель, обеспечивающий получение логических функций ИЛИ — НЕ (на коллекторе VТ2) и ИЛИ (на коллекторе VТЗ). В качестве генератора тока используется высокоомный резистор R5, включенный в объединенную эмиттерную цепь транзисторов VТ1, VТ2 и VТЗ. Источник опорного напряжения выполнен на транзисторе VТ4 и диодах VD1 и VD2. Опорное напряжение, уровень которого находится примерно посередине между уровнями, соответствующими 0 и 1, подается на базу транзистора VТЗ, поэтому транзистор VТЗ будет закрыт, если хотя бы на один из входов подано напряжение более высокого уровня (логическая 1) и открыт, если на всех входах имеется напряжение низкого уровня (логический 0). Логическая информация с коллекторов VТ2 и VТЗ поступает на базы выходных эмиттерных повторителей, выполненных на транзисторах VТ5 и VТ6. Эмиттерные повторители служат для увеличения нагрузочной способности ЛЭ и смещения уровней выходных напряжений для совместимости ЛЭ данной серии по входу и выходу.

Представителями ЛЭ ЭСЛ являются интегральные микросхемы 500-й серии.

Достоинством ЛЭ ЭСЛ является хорошо отлаженная технология их производства, обеспечивающая достаточно высокий процент выхода годных микросхем и их сравнительно низкую стоимость. Элементы ЭСЛ имеют более высокое быстродействие по сравнению с ЛЭ ТТЛ. Благодаря этому они получили широкое распространение в быстродействующей и высокопроизводительной вычислительной технике. Дифференциальные каскады ЛЭ ЭСЛ обеспечивают высокую помехоустойчивость, стабильность динамических параметров при изменении температуры и напряжения источников питания, постоянное, не зависящее от частоты переключения, потребление тока.

Недостатком ЛЭ ЭСЛ является высокая потребляемая мощность.

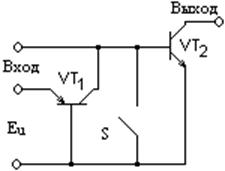

Логические элементы И2Л. ЛЭ И2Л выполняются в виде цепочки транзисторов с инжекционным питанием. Отличительной особенностью таких транзисторов по сравнению с БТ является наличие дополнительного электрода — инжектора. В этой структуре можно выделить два транзистора: горизонтальный токозадающий и вертикальный переключающий, соединенные так, как показано на рис. 5.11, б. Роль электронного ключа S обычно выполняет структура БТ, включенного с ОЭ и работающего в ключевом режиме.

Рис. 5.11. Принципиальная схема инвертора с инжекционным питанием

Смещение инжекторного перехода в прямом направлении достигается подачей на инжектор p-типа положительного напряжения, равного 1...1,5 В. С помощью электронного ключа S база транзистора VТ2 может подключаться к эмиттеру этого транзистора или к генератору тока (коллектору T1). Если ключ разомкнут (при этом входное напряжение имеет высокий уровень), то почти весь ток генератора поступает в базу транзистора VТ2. Транзистор открыт и насыщен, и его выходное напряжение составляет единицы или десятки милливольт (при условии, что к коллектору подключена нагрузка). При замкнутом ключе S почти весь ток генератора тока течет через ключ и лишь незначительная его часть поступает в базу транзистора VТ2. Транзистор находится в активном режиме вблизи области отсечки. Напряжение коллектора транзистора в этом режиме соответствует высокому уровню — примерно 0,8 В.

Таким образом, транзистор с инжекционным питанием можно рассматривать как инвертор или ЛЭ, выполняющий операцию НЕ.

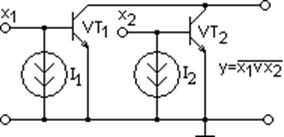

На рис. 5.12 показана схема ЛЭ ИЛИ — НЕ на два входа. При поступлении логических нулей на оба входа транзисторы VТ1 и VТ2 закрыты и на выходе образуется логическая 1. Если хотя бы на один из входов поступает логическая 1, то соответствующий транзистор открыт и насыщен и на выходе, являющемся объединением всех коллекторов, устанавливается логический 0.

Рис. 5.12. Упрощенная схема ЛЭ 2ИЛИ – НЕ инжекционной логики

Достоинствами ЛЭ И2Л являются высокая степень интеграции, большое быстродействие, способность работать при очень малых токах (единицы наноампер) и малых значениях питающих напряжений.

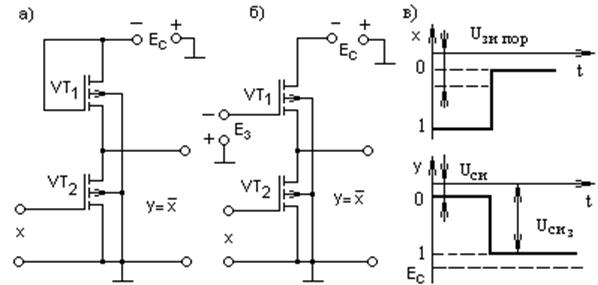

5.5. Базовые логические элементы на МДП- и КМДП-структурах. Базовым элементом логических ИМС на МДП-транзисторах является инвертор (элемент НЕ). На рис. 5.13 показаны схемы инверторов на МДП-транзисторах с каналом p-типа с одним (а) и двумя (б) источниками питания.

Рис. 5.13. Схемы инверторов на МДП-транзисторах (а, б) и графики входных и выходных напряжений (в)

Транзисторы VT1 обеих схем имеют более узкие

и длинные каналы по сравнению с транзисторами VТ2. Поэтому

если оба транзистора VТ1 и VТ2 открыты, то ![]() .

Если

.

Если ![]() , т.е.

, т.е. ![]() ,

то транзисторы VТ2 оказываются открытыми. Так как при этом

,

то транзисторы VТ2 оказываются открытыми. Так как при этом ![]() , то напряжение на выходе близко к

нулю (рис. 5.13, в).

, то напряжение на выходе близко к

нулю (рис. 5.13, в).

Если ![]() , т. е.

, т. е. ![]() , то транзисторы VТ2

закрываются, а транзисторы VТ1 находятся на грани запирания. При этом

, то транзисторы VТ2

закрываются, а транзисторы VТ1 находятся на грани запирания. При этом ![]() и на выходе устанавливается напряжение

с низким отрицательным уровнем, соответствующим логической 1.

и на выходе устанавливается напряжение

с низким отрицательным уровнем, соответствующим логической 1.

Включение в цепь затвора транзистора VT1

дополнительного источника напряжения ![]() повышает

помехоустойчивость ЛЭ.

повышает

помехоустойчивость ЛЭ.

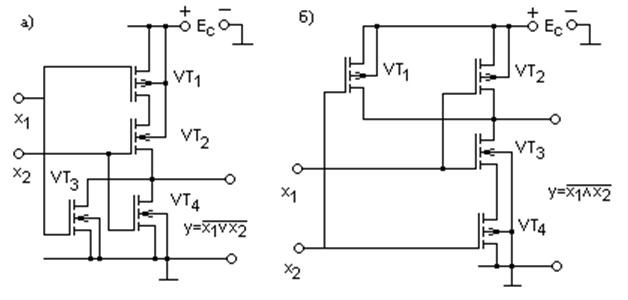

На рис. 5.14, а показана схема двухвходового ЛЭ ИЛИ — НЕ, выполненного на комплементарных МДП-транзисторах. Параллельно соединенные транзисторы VТЗ и VТ4 с каналом n-типа являются управляющими, а транзисторы VТ1 и VТ2 с каналом p-типа — нагрузочными. Управляющие транзисторы образуют нижнее, а нагрузочные — верхнее плечо делителя, с которого снимается выходное напряжение.

Рис. 5.14. Схемы логических элементов ИЛИ — НЕ (а) и И — НЕ (б) на КМДП-транзисторах

Если на входах ![]() и

и

![]() напряжение низкого уровня:

напряжение низкого уровня: ![]() , то транзисторы VТЗ и

VТ4 закрыты. Исток транзистора VТ1 с каналом p-типа

подключен к плюсу источника

, то транзисторы VТЗ и

VТ4 закрыты. Исток транзистора VТ1 с каналом p-типа

подключен к плюсу источника ![]() , поэтому напряжение его затвора

, поэтому напряжение его затвора ![]() и

превышает по абсолютному значению пороговое напряжение. Транзистор VТ1

открыт, сопротивление его канала мало и напряжение истока транзистора VТ2

близко к напряжению

и

превышает по абсолютному значению пороговое напряжение. Транзистор VТ1

открыт, сопротивление его канала мало и напряжение истока транзистора VТ2

близко к напряжению ![]() . Следовательно, транзистор VТ2 также

открыт, и сопротивление верхнего плеча оказывается значительно меньше, чем

сопротивление нижнего плеча. На выходе устанавливается напряжение высокого

уровня, близкое к напряжению источника питания.

. Следовательно, транзистор VТ2 также

открыт, и сопротивление верхнего плеча оказывается значительно меньше, чем

сопротивление нижнего плеча. На выходе устанавливается напряжение высокого

уровня, близкое к напряжению источника питания.

Если хотя бы на один вход ![]() или

или

![]() поступает напряжение высокого

уровня, то соответствующий транзистор нижнего плеча открывается, а верхнего

плеча — закрывается. На выходе образуется напряжение низкого уровня, близкое к

нулю.

поступает напряжение высокого

уровня, то соответствующий транзистор нижнего плеча открывается, а верхнего

плеча — закрывается. На выходе образуется напряжение низкого уровня, близкое к

нулю.

В логических элементах И — НЕ КМДП-ТЛ (рис. 5.14, б)

управляющие МДП-транзисторы с каналом n-типа VТЗ и VТ4

включены последовательно, а нагрузочные с каналами p-типа —

параллельно. Сопротивление нижнего плеча будет мало в том случае, если открыты

оба транзистора VТЗ и VТ4, т.е. когда на входах ![]() и

и

![]() действуют напряжения,

соответствующие логическим единицам. При этом

действуют напряжения,

соответствующие логическим единицам. При этом ![]() и

соответствует логическому нулю. Если на одном из входов будет напряжение

низкого уровня, то один из транзисторов VТ1 или VТ2

открыт, а один из транзисторов VТЗ или VТ4 закрыт. При этом сопротивление верхнего плеча значительно

меньше, чем сопротивление нижнего плеча, и уровень выходного напряжения

соответствует логической единице.

и

соответствует логическому нулю. Если на одном из входов будет напряжение

низкого уровня, то один из транзисторов VТ1 или VТ2

открыт, а один из транзисторов VТЗ или VТ4 закрыт. При этом сопротивление верхнего плеча значительно

меньше, чем сопротивление нижнего плеча, и уровень выходного напряжения

соответствует логической единице.

Логические элементы КМДП-ТЛ отличаются малым

потреблением мощности (десятки нановатт), достаточно высоким быстродействием

(до 10 МГц и более), высокими помехоустойчивостью и коэффициентом использования

напряжения источника питания (![]() ). Их недостатком

является большая сложность изготовления по сравнению с ЛЭ МДП-ТЛ.

). Их недостатком

является большая сложность изготовления по сравнению с ЛЭ МДП-ТЛ.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.