По данной таблице легко построить карту Карно и записать формулу.

|

|

X2 |

|

|

X1 |

0 |

1 |

|

1 |

0 |

![]()

![]()

![]()

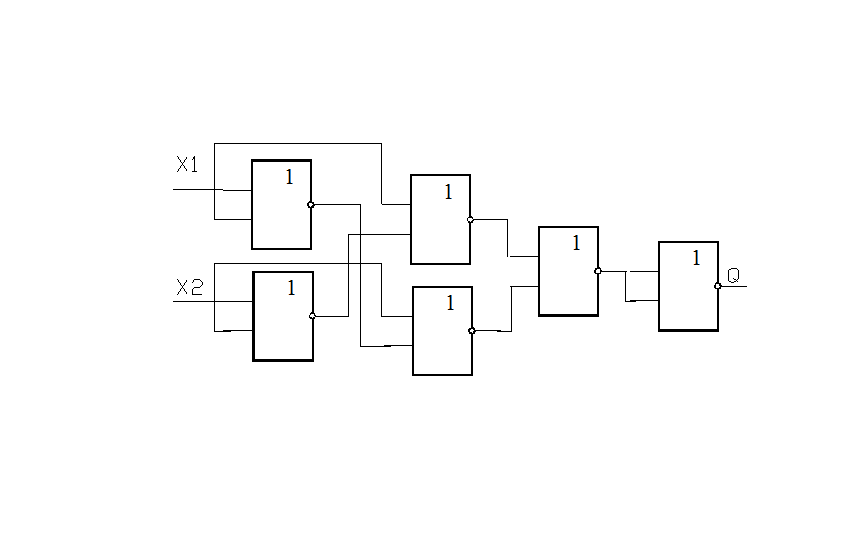

Y=(X1↓X2)↓(X1↓X2),

По этой формуле можно построить схему сумматора.

|

||||||||

|

||||||||

|

||||||||

|

||||||||

|

||||||||

|

||||||||

|

||||||||

|

||||||||

|

||||||||

|

||||||||

Рисунок 1.7.Сумматор.

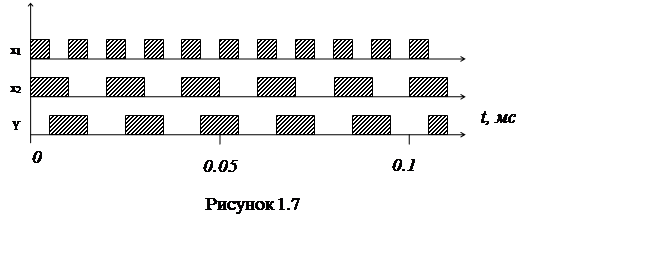

Наглядная работа двухвходового сумматора показана на временной диаграмме, рисунок 1.5.3

|

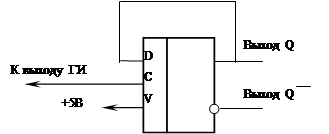

Делитель частоты — устройство, предназначенное для деления частоты следования тактовых импульсов генератора. По заданию коэффициент деления делителя равен двум. В качестве такого делителя можно использовать один D–триггер, работающий как счётчик с коэффициентом счёта 2. Схема счётчика приведена на рисунке 1.2. С выхода делителя сигнал поступает на входы сумматора (описание см. выше).

На принципиальной схеме блок делителя частоты обозначен ДЧ. Временные диаграммы работы делителя частоты приведены в приложении 1 на рисунке 3.

|

Рисунок 1.8. Делитель частоты.

ГИ

|

||||||||||||||||||||||

![]() 0

0

ДЧ

|

||||||||||||

![]() 0

0

Рисунок 1.9. Временные диаграммы делителя частоты.

Синтезированное дискретное устройство представляет собой в конечном счёте сумматор двух четырёхразрядных двоичных чисел. Для последовательной генерации двоичных чисел используется счётчик и делитель частоты. Рассмотрим работу устройства подробнее.

Генератор ГИ формирует сигнал в виде прямоугольных импульсов. С выхода ГИ сигнал поступает на счётчик СТ, где происходит счёт импульсов и как следствие происходит как бы генерация некоторого двоичного числа (при этом двоичное число представлено в коде 8421). С выходов счётчика полученное двоичное число поступает на входы преобразователя кода ПК, где происходит преобразование числа из кода 8421 в код с избытком 3. Далее с выходов ПК двоичное число передаётся на соответствующие 4 входа сумматора. На другой вход подаётся сигнал с делителя частоты ДЧ. Таким образом происходит суммирование числа с преобразователя кода с числом 1111. Для синхронной работы, т.е. для одновременного прихода сигнала с ПК и ДЧ на сумматор, сигналы на счётчик импульсов и через ДЧ на сумматор подаются от одного генератора. Работа всех перечисленных блоков описана в разделах 1.1–1.5.

В ДУ применены микросхемы структуры КМДП серии К561 и К176. Микросхемы данной структуры обладают работоспособностью в широком диапазоне питающих напряжений, высокую помехозащищённость, высокую нагрузочную способность. Основным преимуществом КМДП–микросхем является малая статическая мощность, потребляемая от источника питания (порядка нановатт). Некоторые параметры использованных микросхем приведены в таблице 1 приложения 2.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.