Помимо задания тактовой частоты, генератор может служить для синхронизации сигналов READY с тактовыми сигналами процессора. В данной МПС нет необходимости в использовании сигналов READY, т.к. все устройства успевают осуществить обмен данными с процессором без введения дополнительных тактов ожидания. Поэтому, входы R`DY1,RDY2 подключены к высокому потенциалу, а входы AEN1,AEN2 подключены к земле, задавая тем самым постоянно готовое состояние системы.

Для обеспечения высокого потенциала на входах RDY1, RDY2, они подключены к UCC через резистор R2. Расчет сопротивления R2 аналогичен расчету сопротивления R3, поэтому в качестве R3 будет использоваться ОМЛТ-0.125–1.5кОм±5%.

Управляющие сигналы ST0 - ST2 с CPU подаются на контроллер системной шины CB, в качестве которого выбрана микросхема К1810ВГ88 - контроллер системной шины. Выходными сигналами контроллера системной шины, являются сигналы чтения/записи памяти и внешних устройств, а также сигналы управления регистрами адреса и буферными регистрами данных, а также выдается сигнал подтверждения прерывания. Схема подключения показана на рис. 8. Назначение выводов микросхемы указано в табл. 3.

Таблица 3

|

Вывод |

Обозначение |

Тип вывода |

Функциональное назначение выводов |

|

1 |

IOB |

Вход |

Управление режимом работы контроллера. |

|

2 |

CLK |

Вход |

Синхронизирующий вход. |

|

19, 3, 18 |

S0 - S2 |

Входы |

Входы сигналов состояния МП. |

|

4 |

DT/R |

Выход |

Сигнала управления работой шинных формирователей. |

|

5 |

ALE |

Выход |

Сигнал стробирования адреса. |

|

6 |

AEN |

Вход |

Управление выдачей сигналов контроллера. |

|

7 |

MRDC |

Выход |

Чтение из памяти. |

|

8 |

AMWTC |

Выход |

Опережающий сигнал записи в память. |

|

9 |

MWTC |

Выход |

Запись в память. |

|

11 |

IOWC |

Выход |

Сигнал вывода в устройство ввода вывода. |

|

12 |

AIOWC |

Выход |

Опережающий сигнал вывода в устройство ввода вывода. |

|

13 |

IORC |

Выход |

Сигнал ввода из устройства ввода вывода. |

|

14 |

INTA |

Выход |

Подтверждение прерывания. |

|

15 |

CEN |

Вход |

Сигнал управления DEN и PDEN. |

|

16 |

DEN |

Выход |

Управление состоянием "включено" шинных формироват. |

|

17 |

MCE/POEN |

Выход |

Сигнал управления. |

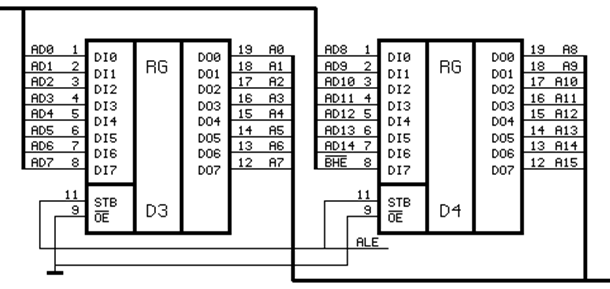

Сигналы AD0 - AD14, BHE с CPU поступают на RGA - буферный регистр адреса. В качестве RGA выберем 2 микросхемы КР580ИР82, назначение выводов этой микросхемы указано в табл. 4. Схема подключения показана на рис. 9. В разрабатываемой МПС решено использовать 14 младших разрядов адреса (согласно п. 3.2 нам этого достаточно). Для определения, к какому банку памяти идет обращение, мы используем сигнал BHE. Т. к. он формируется в том же интервале времени, что и адресные сигналы, то его также необходимо зафиксировать в защелке. Вход ОЕ, регистра адреса заземляем, т.к. адрес должен находиться на ША весь цикл работы. На вход STB подаем сигнал ALE с выхода контроллера системной шины.

|

Рис. 8. Функциональная схема контроллера системной шины CB. |

|

|

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.