ИОЗУ 512х8 (элементы D47 … D50) предназначено для записи 512 входящих канальных байтов и их считывания для передачи в исходящие ИКМ-линии. ОЗУ состоит из двух банков, на которые подаются управляющие и адресные сигналы с мультиплексора 1. Если в один из банков в определенный цикл 125 мкс происходит запись входящих канальных байтов, то из другого происходит считывание и наоборот.

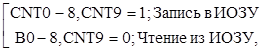

Переключение банков осуществляется по сигналу CNT9 частотой 4 кГц.

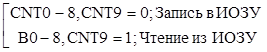

Мультиплексор 1 формирует управляющие и адресные сигналы для информационного ОЗУ:

A1 =

A2 =

где В0 – 8 – 9-разрядный код адреса входящего канального байта при передаче его в исходящие ИКМ-линии.

9 разрядный адрес информационного ОЗУ определяет временное и пространственное положение входящих канальных байтов и задается сигналами CNT0–CNT8. Этот адрес может быть определен следующим образом:

- младшие четыре разряда представляются как номер ИКМ-линии, и производится циклический сдвиг влево с переносом старшего третьего разряда в нулевой;

- старшие пять разрядов представляются как номер канального интервала;

- к полученному 9-разрядному коду прибавляется начальное смещение 12Н;

- инвертируется младший разряд.

Пример 1. Вычисление кода адреса входящего байта:

а) 0-й ИКМ-тракт, 7-й канальный интервал

|

0000 0000 |

– номер ИКМ-линии – циклический сдвиг с переносом |

|

|

номер канального интервала |

00111 0000 00001 0010 |

– начальное смешение 12Н |

|

01000 0010 01000 0011 |

– инверсия младшего разряда = 83Н |

б) 15-й ИКМ-тракт, 0-й канальный интервал

|

1111 1111 |

– номер ИКМ-линии – циклический сдвиг с переносом |

|

|

номер канального интервала |

00000 1111 00001 0010 |

– начальное смещение 12Н |

|

00010 0001 00010 0000 |

= 20Н |

В адресном ОЗУ 512х9 хранятся 512 адресов ВО-8, которые определяют положение входящих канальных байтов и могут быть вычислены по приведенному выше алгоритму. Запись этого кода осуществляется с шины В по сигналу EWR1. Момент считывания или записи каждого из 512 адресов (один раз за цикл 125 мкс) определяет положение исходящего байта и задается сигналами CNT 0–8, которые подаются на адресные входы адресного ОЗУ.

Таким образом, адрес адресного ОЗУ однозначно определяет положение исходящего байта и может быть вычислен аналогично алгоритму вычисления кода адреса входящего байта за исключением пункта 3: вместо сложения со смещением 12Н необходимо вычесть смещение 13Н.

Пример 2. Вычисление кода адреса исходящего байта:

а) 9-й ИКМ-тракт, 31-й канальный интервал

|

1001 0011 |

||

|

_11111 0011 00001 0011 |

||

|

11110 0000 11110 0001 |

= 1Е1Н |

б) 0-й ИКМ-тракт, 10-й канальный интервал

|

0000 0000 |

||

|

_01010 0000 00001 0011 |

||

|

01000 1101 01000 1100 |

= 8СН |

Цифровой компаратор 2 вырабатывает при совпадении кода на шине А и кода СNT0-8 следующие сигналы длительностью 244 мс:

- сигнал записи EWR1 кода адреса входящего байта при МОDЕ = 1;

- сигнал совпадения СС при любом значении сигнала МОDЕ.

Мультиплексор-конвертор исходящих ИКМ-линий тактируется частотами 2048F1 и 2048F2 и осуществляет преобразование параллельной информации (канальные байты) в последовательную (ИКМ-линии).

Передатчик исходящих ИКМ-линий служит для подключения исходящих ИКМ-линий к магистрали при сигнале DЕNЗ = 1. Мультиплексор-конвертор 1 тактируется частотой 2048F2 и преобразует тестовый байт в канальный байт тестовой входящей ИКМ-линии. Временное и пространственное положение этого байта определяется сигналом DЕN2 и 4-разрядным кодом 10-3 из регистра 3.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.