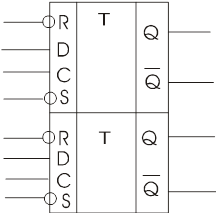

2.6 Схема D-триггера

Схема D-триггера К155ТМ2 электрическая принципиальная приведена на рис.13.

Рис.13. Схема электрическая принципиальная D-триггера К155ТМ2.

![]()

![]() Микросхема

К155ТМ2 серии ТТЛ содержит два независимых D-триггера.

Микросхема

К155ТМ2 серии ТТЛ содержит два независимых D-триггера.

![]() У

каждого триггера есть выходы D, S, R, а также комплементарные выходы Q и Q . Логика работы микросхемы показана в таблице 7.

У

каждого триггера есть выходы D, S, R, а также комплементарные выходы Q и Q . Логика работы микросхемы показана в таблице 7.

Таблица 7. Состояния триггера микросхемы К155ТМ8.

|

работы |

Вход |

Выход |

||||

|

|

|

C |

Di |

Qi |

Qi |

|

|

Установка |

0 |

1 |

Х |

Х |

1 |

1 |

|

Сброс |

1 |

0 |

X |

X |

0 |

1 |

|

Неопределенность |

0 |

0 |

X |

X |

1 |

1 |

|

Загрузка 1 |

1 |

1 |

á |

1 |

1 |

0 |

|

Загрузка 0 |

1 |

1 |

á |

0 |

0 |

1 |

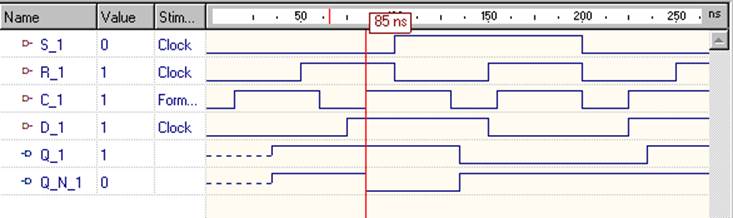

Рис.14. Временная диаграмма D-триггера

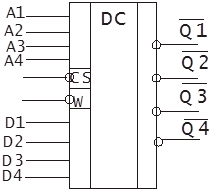

2.7 Схема ОЗУ

Микросхема К155РУ2 (рис. 15.) – высокоскоростное ОЗУ с емкостью 64 бит. Данные в ОЗУ можно записывать и считывать. При считывании информации из ОЗУ она не разрушается. Ячейки в памяти организованы в матрицу имеющую 16 рядов и четыре колонки, что соответствует логической организации 16 слов по четыре бита каждое.

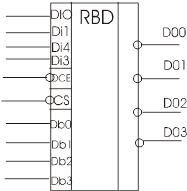

Схема микросхемы К155РУ2 приведена на рис.15

Рис. 15. Схема микросхемы К155РУ2

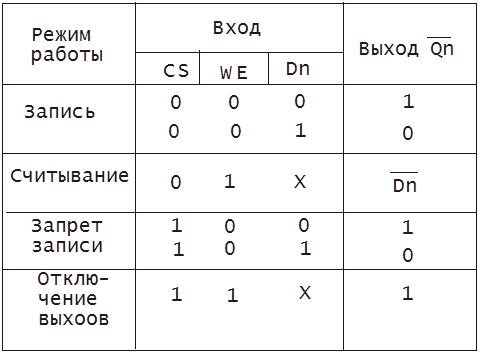

Логика работы микросхемы показана в таблице 8.

Таблица 8. Состояние ОЗУ К155РУ2.

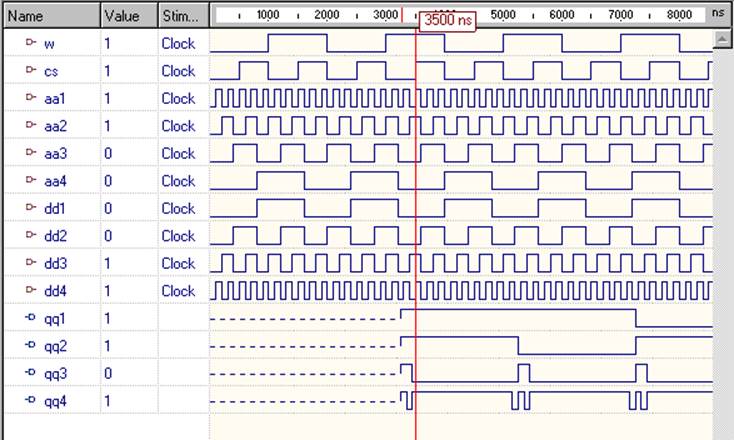

Временная диаграмма работы микросхемы К155РУ2 показана на рисунке 16.

Рис. 16. Временная диаграмма работы микросхемы К155РУ2.

2.8 Микросхема К589АП26.

Микросхема К589АП26 шинный формирователь с инверсией, является параллельным двунаправленным формирователем сигналов для управления магистралями (шинами) в цифровых вычислительных устройствах.

Условное графическое обозначение микросхемы К589АП26 приведено на рисунке 17.

Рис. 17. Условное графическое обозначение микросхемы К589АП26.

Логика работы схемы приведена в таблице 9.

Таблица 9.

Временная диаграмма работы микросхемы К589АП26 приведена на рис.18.

Рис.18. Временная диаграмма работа микросхемы К589АП26.

3. МОДЕЛИРОВАНИЕ

3.1 Моделирование элементов схемы

Модель элемента К155ЛА2

--- File: k155La2.vhd

-- created by Design Wizard: 05/13/02 19:52:35

-library IEEE;

use IEEE.std_logic_1164.all;

entity k155La2 is

port (

x1: inout STD_LOGIC;

x2: inout STD_LOGIC;

x3: inout STD_LOGIC;

x4: inout STD_LOGIC;

x5: inout STD_LOGIC;

x6: inout STD_LOGIC;

x7: inout STD_LOGIC;

x8: inout STD_LOGIC;

y1: out STD_LOGIC

);

end k155La2;

architecture k155La2 of k155La2 is

begin

-- <<enter your statements here>>

Process (x1,x2,x3,x4,x5,x6,x7,x8) begin

y1<=not (x1 and x2 and x3 and x4 and x5 and x6 and x7 and x8) after 22 ns;

end process;

end k155La2;

Модель элемента К155ЛА3

--- File: c:\my designs\Bal\SRC\K155La3.VHD

-- created by Design Wizard: 04/19/02 12:18:22

-library IEEE;

use IEEE.std_logic_1164.all;

entity K155La3 is

port (

c1: in STD_LOGIC;

c2: in STD_LOGIC;

Q1: out STD_LOGIC

);

end K155La3;

architecture K155La3 of K155La3 is

begin

-- <<enter your statements here>>

process (c1,c2)

begin

Q1<=c1 nand c2 after 22 ns;

end process;

end K155La3;

Модель элемента К155ЛА6

--- File: K155La6.vhd

-- created by Design Wizard: 05/13/02 20:29:18

-library IEEE;

use IEEE.std_logic_1164.all;

entity K155La6 is

port (

a1: in STD_LOGIC;

a2: in STD_LOGIC;

a3: in STD_LOGIC;

a4: in STD_LOGIC;

b1: out STD_LOGIC

);

end K155La6;

architecture K155La6 of K155La6 is

begin

-- <<enter your statements here>>

Process (a1,a2,a3,a4)

Begin

b1<= not(a1 and a2 and a3 and a4)after 22 ns;

End process;

end K155La6;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.