3. ПРИНЦИПИАЛЬНАЯ СХЕМА

3.1. Выбор схемотехники основных узлов.

На этапе проектирования структуры системы мы разработали архитектуру системы, не вдаваясь в детальное рассмотрение всех её узлов.

Дальнейшее проектирование и доведение схемы до принципиального уровня надо, наверное, начинать с постоянного запоминающего устройства и динамического запоминающего устройства.

3.1.1. постоянное запоминающее устройство.

Постоянные запоминающие устройства (ПЗУ) предназначены для хранения программ, констант, таблиц, тестов и другой информации, которая не изменяется в процессе работы устройств. Запись информации в ПЗУ производится заблаговременно до её примения. Записанная информация может быть произвольной.

По своей логической структуре ПЗУ является кодовым преобразователем: входной код (адрес) однозначно преобразуется в любой заданный выходной код.

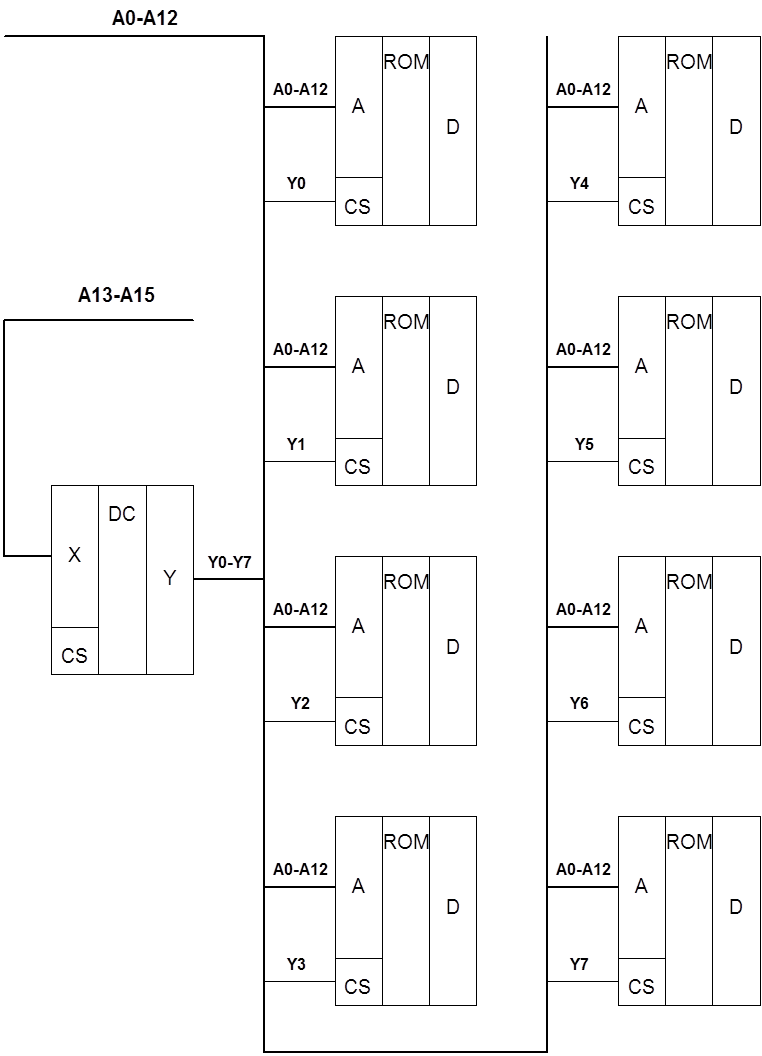

Микросхема ПЗУ приспособлена для наращивания, как числа слов, так и числа разрядов хранимых слов. Для увеличения числа хранимых слов адресные входы микросхем соединяют параллельно и рассматривают как младшие разряды входного адреса. Старшие разряды входного адреса поступают на дешифратор, выходы которого соединяют с входами CS соответствующих микросхем. Выходы одноименных разрядов микросхем ПЗУ соединяют.

В данной схеме были выбраны постоянное запоминающее устройство серии КР568РЕ2 (DD6.1…DD6.8).

3.1.2. оперативное запоминающее устройство.

Как правило, микросхемы ОЗУ содержат на одном кристалле матрицу ЗЭ (накопитель), дешифраторы адреса, формирователи, усилители считывания и другие схемы управления, необходимые для функционирования ОЗУ.

В данной схеме были выбраны оперативное запоминающее устройство китайского производства серии СС6264 (DD7.1…DD7.8).

3.1.3. преобразователь уровени.

Для преобразования уровней ТТЛ-RS232 использована микросхема ICL232 (DD1). Эта микросхема позволяет от одного питающего напряжения 5В сформировать на выходе стандартные уровни интерфейса RS-232.

|

Рис 3.1 Схема наращивания ПЗУ.

3.2. Описание принципиальной схемы

После того, как были разработаны схемы подключения ОЗУ и ПЗУ, принципиальная схема была доработана до окончательного варианта (см. Схему электрическую принципиальную).

Итак, как уже говорилось выше, все функции управления и адресации взял на себя микроконтроллер DD2. Это микроконтроллер INTEL 8051C [35].

Микроконтроллер имеет встроенный последовательный порт, использование которог позволяет упростить организацию процесса обмена с ЭВМ.

Включение микроконтроллера выполнено следующим образом: порты 1 и 2 используются для выдачи адреса, остальные порты выдают и принимают управляющие сигналы. Порт 1, помимо функции выдачи адреса, служит также для передачи данных.

Регистры DD3, DD5 служит для буферизация и переключения между сигналы адреса и данных на основную магистраль адреса/данный.

Для хранения промежуточной информации используется оперативное запоминающее устройство DD7.1…DD7.8, объёмом 64Кбайт. Ёмкость ОЗУ выбиралась из следующих соображений. Для хранения одного спектра матрица размером 32*32 требуется 1024 байт, выходный матриц размером 25 байт, каждая строка по меньшее мерий имеют иероглифов по 50 и так общая сумма (1024+25)*50=52450 байт. Таким образом, необходимый объём ОЗУ составляет 52450 байт. Для ОЗУ выбрана микросхема СС6264. Время выборки адреса её 250 нс.

Одна микросхема СС6264 содержит 8 Кбайта. Поэтому используется 8 корпуса. Выбор нужного корпуса осуществляется с помощью дешифратора DD4, который выдаёт сигналы Q0…Q7, подаваемые на дополнительные входы CS микросхем памяти.

После того, как устройство отработает процесс сбора информации, её необходимо переписать в энергонезависимую память. Доступ к главной магистрали данных осуществляется через элемент DD3 и DD5.

Итак, весь блок обработки информациии состоит из микроконтроллера, ОЗУ, ПЗУ, дешифратора, преобразователь уровень ТТЛ-RS232 и регистрового элемента.

Мы выбрали микросхему памяти КР568РЕ2. Она обладает следующими характеристиками:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.