Для построения сумматора с разрядностью 24 необходимо использовать 6 АЛУ. При этом, можно использовать структуру с последовательным переносом, когда перенос с выхода одного АЛУ поступает на вход переноса другого АЛУ, что значительно снижает быстродействие. При использовании структуры с параллельным переносом выходные сигналы P(распространение переноса) и G(генерация переноса) поступают с выхода каждого АЛУ на входы устройства переноса. Далее с выхода устройства переноса на входы каждого АЛУ подается перенос. Таким образом, операция происходи как бы в три этапа: сложение операндов и генерация каждым АЛУ сигналов P и G, формирование устройством обработки переноса переносов для каждого АЛУ, корректировка результата сложения каждым АЛУ в соответствии с входным переносом.

Для последовательного переноса время сложения можно оценить по следующей формуле:

Tсл. общ.=Tсл. АЛУ*число АЛУ (5)

Для параллельного переноса время сложения можно оценить по формуле:

Tсл. общ.=Tформирования P,G+Tформирования переноса+Tсложения (6)

С упрощением, что все величины в формуле (6) примерно равны и равняются величине в формуле (5), для 24Х разрядного сумматора время вычисления с использованием параллельного переноса в 2 раза меньше, чем при использовании последовательного переноса (точный расчет параметров, использованный при синтезе см. в разделе синтеза управляющего автомата).

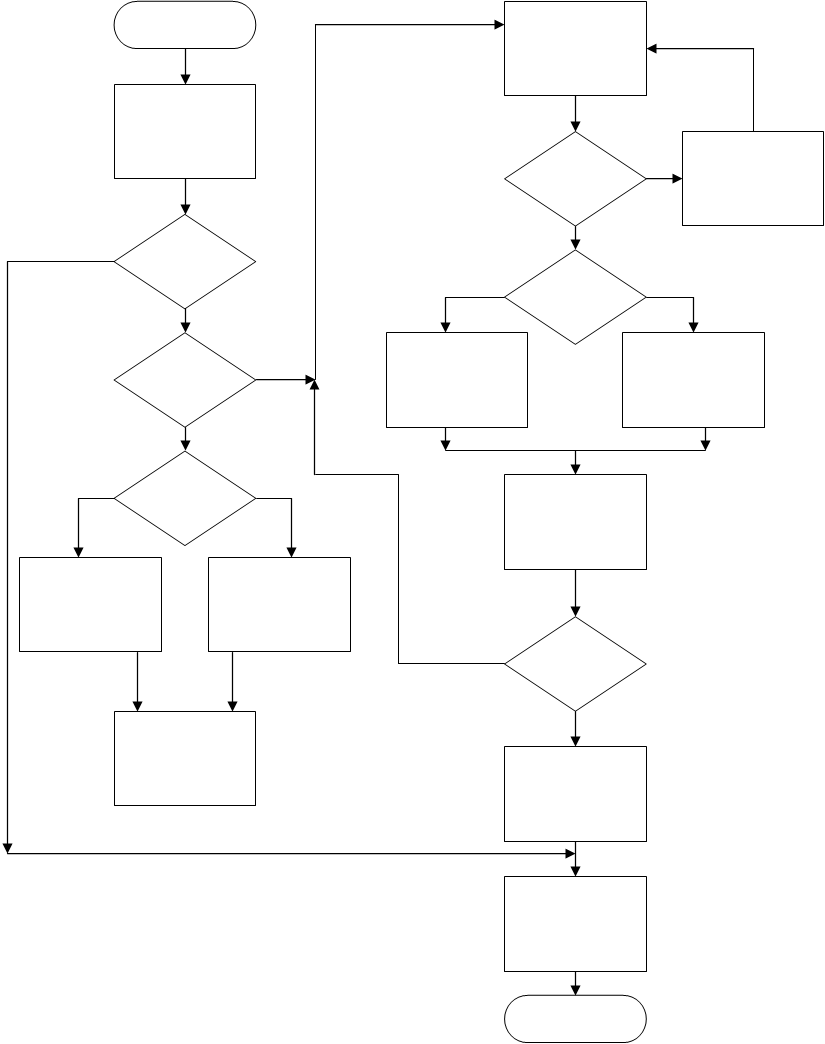

Для проектирования функциональной схемы составим регистровую

блок-схему алгоритма.

Для проектирования функциональной схемы составим регистровую

блок-схему алгоритма.

Рис. 1. Регистровая блок-схема.

Согласно регистровой блок схеме построим функциональную схему, причем блок №17 и №18, не несет в себе вычислительной функции. На этих этапах происходит формирование знака результата и обработка действий приведения аргумента в первую или четвертую четверть, произведенную ранее (эти действия возложены на управляющий автомат).

![]() Работу устройства

можно разделить на следующие этапы:

а) загрузка аргумента функции

б) приведение аргумента в 1ую или 4ую четверть

в) основной вычислительный цикл, включающий в себя циклы сдвига

г) формирование конечного результата

д) выдача результата работы внешнему устройству

Работу устройства

можно разделить на следующие этапы:

а) загрузка аргумента функции

б) приведение аргумента в 1ую или 4ую четверть

в) основной вычислительный цикл, включающий в себя циклы сдвига

г) формирование конечного результата

д) выдача результата работы внешнему устройству

Рассмотрим работу в соответствии приведенными выше этапами.

На этапе А на вход управляющего автомата ( вход I2 ИМС MAIN) поступает сигнал достоверности данных (D_READY), которые через буферный элемент INBUF подаются на мультиплексор регистра RO (ROMUX). Далее с приходом очередного синхроимпульса управляющий автомат выдает сигнал выборки входа B на мультиплексоры ROMUX, RYMUX, RXMUX. Выдержав определенное время (время предустановки), управляющий автомат выдает сигнал записи для регистров RO, RY и RX (CPRXRY и CPRO соответственно). После этого, выдержав время удержания данных, управляющий автомат подает сигнал выборки входа А мультиплексоров RO, RY, RX и удерживает его в этом состоянии. Если сигнал D_READY не поступает, то происходит ожидание прихода этого сигнала.

Далее начинается этап Б. На этом этапе, после установления данных на входе АЛУ ALURO управляющий автомат генерирует несколько холостых циклов .с тем, чтобы успел установиться результат на выходе АЛУ и (или) признак ROGP, далее, с приходом очередного синхроимпульса, производится совместный анализ признака ROGP и RO_LOW. Если признак RO_LOW истинен, то происходит переход на этап Г. Если нет, то происходит анализ признака ROGP. Признак ROGP формируется следующим образом: из регистровой блок-схемы видно, что операция, которую производит АЛУ определяется знаком числа, находящегося в регистре RO, если в RO отрицательное число, то ALURO производит операцию арифметического сложения и наоборот. Таким образом, если в регистре RO изначально находится отрицательное число, тогда если к этому числу прибавить +p/2, то, если в RO находится число по модулю большее, чем p/2, то знак числа после операции алгебраического сложения не измениться. Если число было по модулю меньше p/2, то знак изменится на противоположный. В случае когда в регистре RO находится положительное число, все происходит аналогично. Если признак ROGP равняется 1, то результат меньше p/2 и происходит переход к этапу В. В противном случае управляющий автомат выдает импульс записи значения в RO (CPRO), происходит увеличение значения внутреннего счетчика (находится в ИМС MISC) для дальнейшего использования на этапе Г. Этот процесс повторяется до тех пор, пока не произойдет приведение аргумента в первую (в случае, когда аргумент положительный) или четвертую (аргумент меньше 0) четверть.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.