ССП – слово состояние процессора.

С – перенос.

- логические и арифметические:

Z – признак 0.

N – знаковый.

Регистр признаков – регистр состояния процессора.

Формируется слово состояние процессора: C, Z, N.

Дополнительно: перенос из младших разрядов в старший в 10 или 16 системе исчисления; разрешение прерываний.

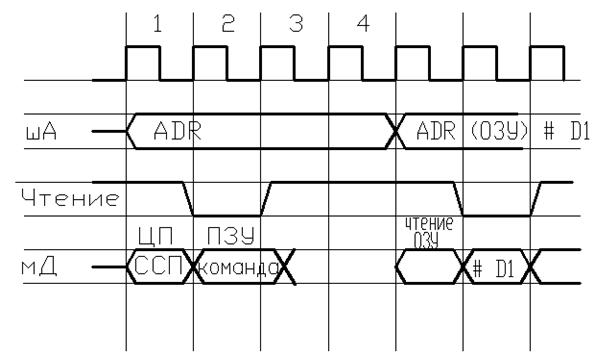

Количество тактов

![]() чтение

чтение

……………….

n. MOV D, # ADR

если #D1 – в ПЗУ, при помощи Ск.

ADR [ПЗУ] #D1, адрес формируется Ск.

Если 3 цикла за место ADR (…) – выставить сам адрес.

Вывод:

1. команда может занимать несколько тактов.

2. цикл может занимать несколько тактов.

§1: Представление информации.

“1” – символическое представление уровня логической единицы.

“0” – символическое представление уровня логического нуля.

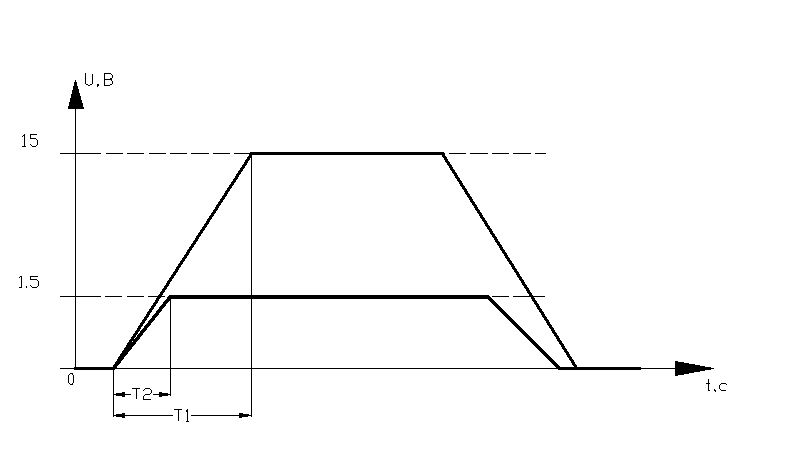

Рис. Состояние и переход сигнала

На рис. уровень логического нуля является напряжение 0В(уровень физического нуля), а уровень логической единицы 1,5 В для одной схемы, и 15В для другой схемы(T2>T1)

Некоторые технологии, работающие со сигналами:

Транзисторно-Транзисторная Логика (ТТЛ):

“1” – 5В

“0” – 0В

Эммитерно-Связанная Логика (ЭСЛ):

“1” – 0В

“0” – -5.2В

Комплементарно Окислитель Проводник (КОП):

“1” – 1.5 ¸ 15В

“0” – 0В

Представление информации на логическом уровне:

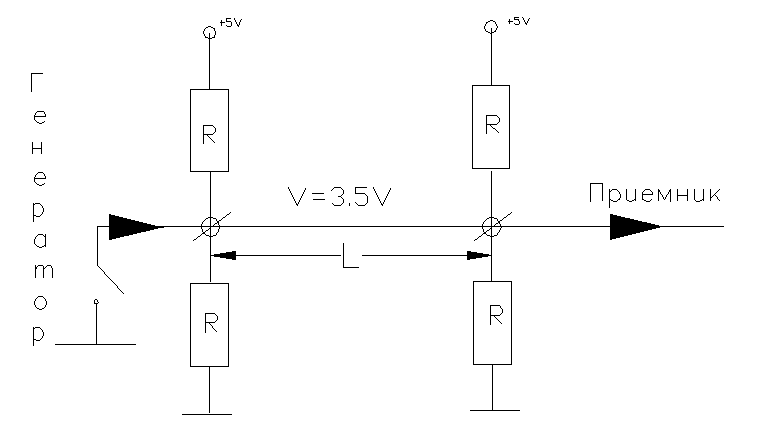

Рис2. Передача сигнала без искажени

Передача согнала без искажения,

происходить, если соблюдается его согласованность.

Передача согнала без искажения,

происходить, если соблюдается его согласованность.

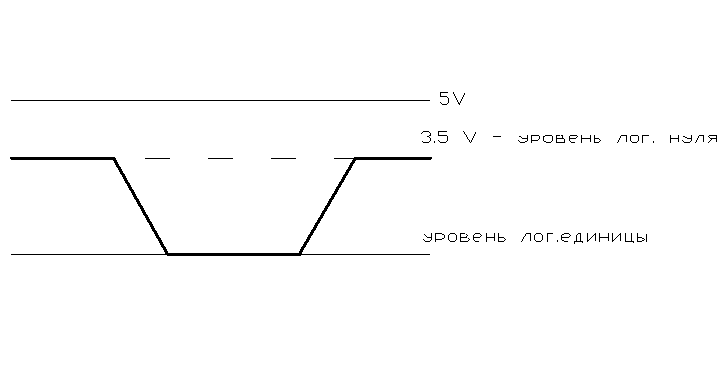

Рис3. Пассивное состояние.

В пассивном состояние уровень лог. единицы соответствует низкому уровню напряжению, с уровнем лог. нуля наоборот.

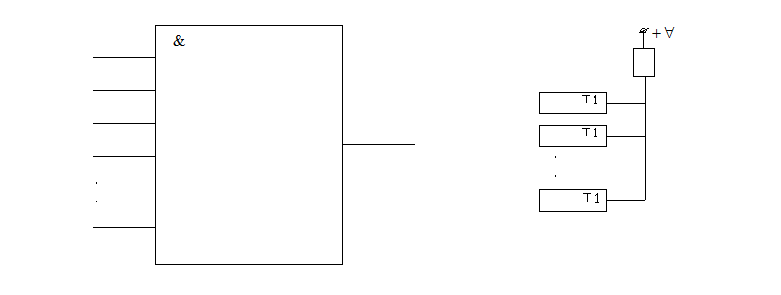

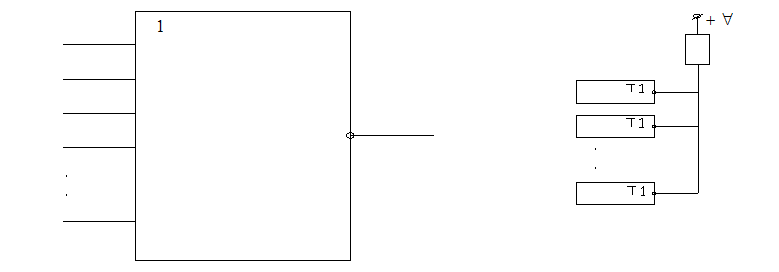

Логические модули:

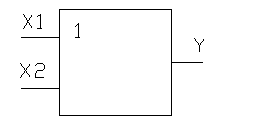

“Умножение(AND)”: “Сложение(OR)”:

“Умножение(AND)”: “Сложение(OR)”:

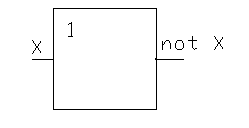

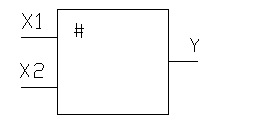

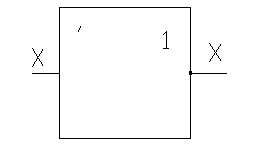

“Отрицающие сложение(XOR)”: “Инвертор(Not)”:

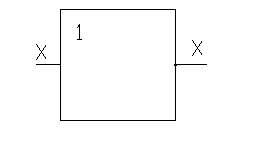

“Повторитель”:

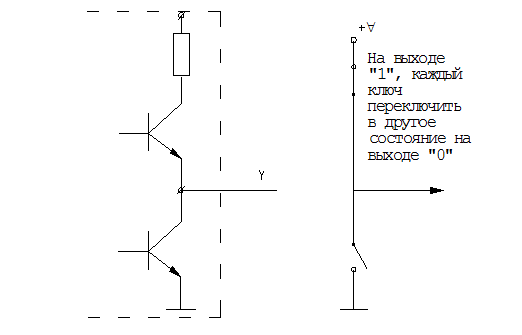

Открытый коллектор:

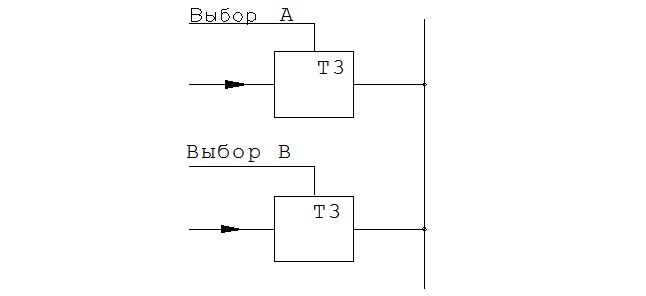

Выбор X – работы транзистора.

a). б).

Рис4.

Открытый коллектор, конструктивно представлен на рис4а., а на рис.4б. представлена упрощенная схема открытого коллектора (один ключ всегда замкнут)

![]() Рассмотри схему рис.4а

Рассмотри схему рис.4а

1). Без верхнего транзистора, обозначается

С помощью такой новой схемы можно реализовать модуль умножения, инвертора

(Примечание: только в данном рисунке, элемент без верхнего транзистора обозначается T1).

![]() 2). Без нижнего транзистора, обозначается]

2). Без нижнего транзистора, обозначается]

3). Элемент с тремя состояниями, обозначается

a). “0” – работает нижний транзистор

b). “1” – работает верхний транзистор

c). не работают оба транзистора

Все канальные приемо-передатчики обладают возможностью перехода в 3-е состоянеие.

Выбор X – выбор работы транзистора.

Триггер – элементарная ячейка памяти. Используется в качестве двоичных элементов памяти, каждый из которых способен хранить бит информации.

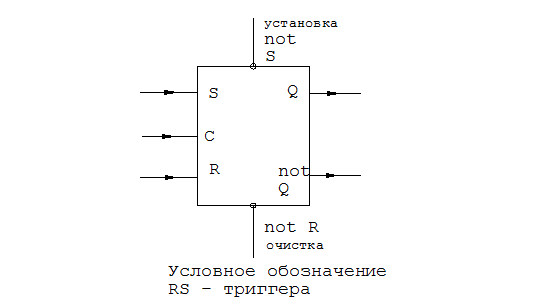

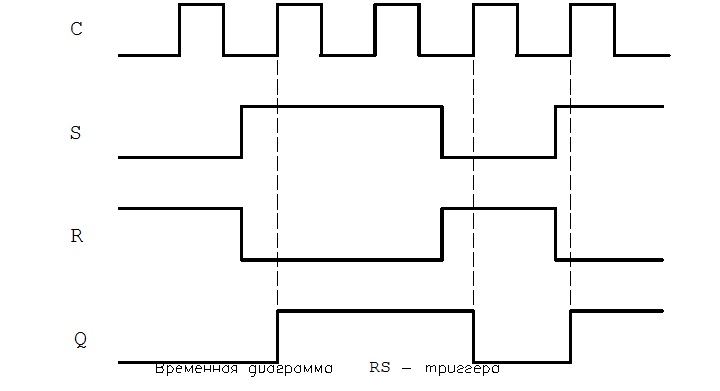

RS триггер:

Входы S и R используются для подачи

сигналов, определяющих последующие состояние триггера, однако сигналы,

приложенные к этим входам, оказывают воздействие на триггер только в моменты

стробирования их синхроимпульсами C. Если на входе R будет “1”, то синхроимпульс переведет триггер в состояние

“0”(сброс). Если на входе S будет “1”, то синхроимпульс

переключит триггер в состояние “1”(установка).

Входы S и R используются для подачи

сигналов, определяющих последующие состояние триггера, однако сигналы,

приложенные к этим входам, оказывают воздействие на триггер только в моменты

стробирования их синхроимпульсами C. Если на входе R будет “1”, то синхроимпульс переведет триггер в состояние

“0”(сброс). Если на входе S будет “1”, то синхроимпульс

переключит триггер в состояние “1”(установка).

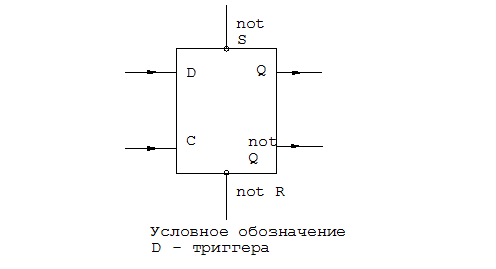

D – триггер:

RS триггер с одним входом данных D.

Если D=1, то синхроимпульс переключит триггер в состояние “1”. Если D=0,

синхроимпульс переключит триггер в

состояние “0”.

синхроимпульс переключит триггер в

состояние “0”.

Примечание: Нельзя подавать больше одного сигнала.

На основе лог. модулей можно организовать сумматоры 1,2,3,.. разрядные. На сумматоры с большой разрядностью уходит много ресурсов(логических модулей).

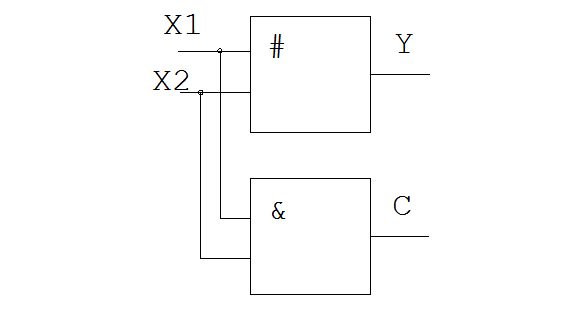

Одноразрядный сумматор:

Двухразрядный сумматор:

Лекция 1

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.