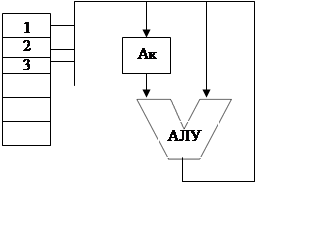

Выражение А + В àC , для того чтобы реализовато его за 1

такт, нужно реализовать 3 потока данных.

, для того чтобы реализовато его за 1

такт, нужно реализовать 3 потока данных.

Используется: СуперЭВМ и некоторые RISC-системы.

|

Этапы реализации операции суммирования:

1). 1 à Ak.

2). 2+ à Ak.

3). Ak à 3.

Использование: intel'овская организация.

|

Этапы реализации выражения:

1). А + В à (AvB)

2). (AvB) à C

Использование : DEC'овская организация.

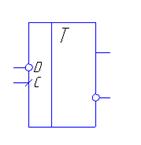

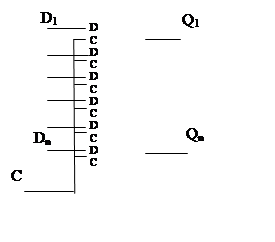

D-триггер.

Определяющий фактор.

С

С

D

Q

Q

Триггер с динамической записью.

Асинхронный D-триггер.

Для задания начального состояния используют R и S входы, такой D-триггер называется асинхронный. R-S входы – для установки или сброса.

Если на S вход подается 0, то Q = 1, а если на R подавать 0, то Q= 0.

Двухступенчатый D-триггер.

![]() Система хлопушка:

Система хлопушка:

С

- активный «1».

![]() D

D

- активный «0».

Q

Если С = 0, то триггер сохраняет свое состояние. Триггер со статической записью.

регистр.

Регистр

Регистр

|

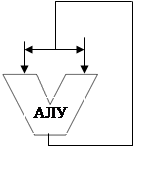

Двухразрядный сумматор.

1).

à A à Ak

1).

à A à Ak

2). à B + à Y

28.09.

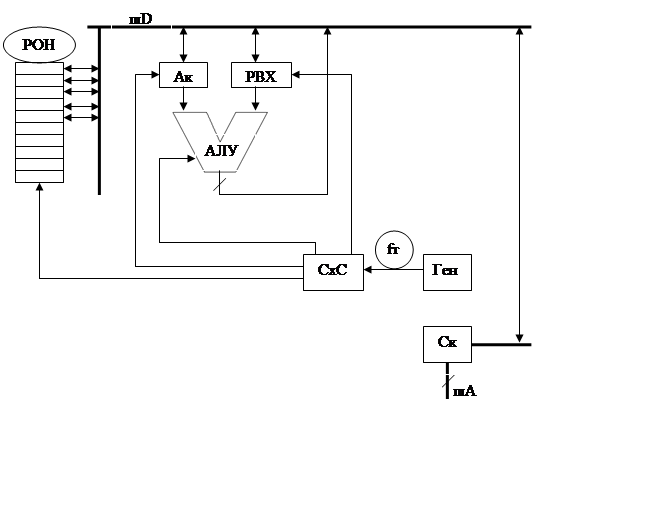

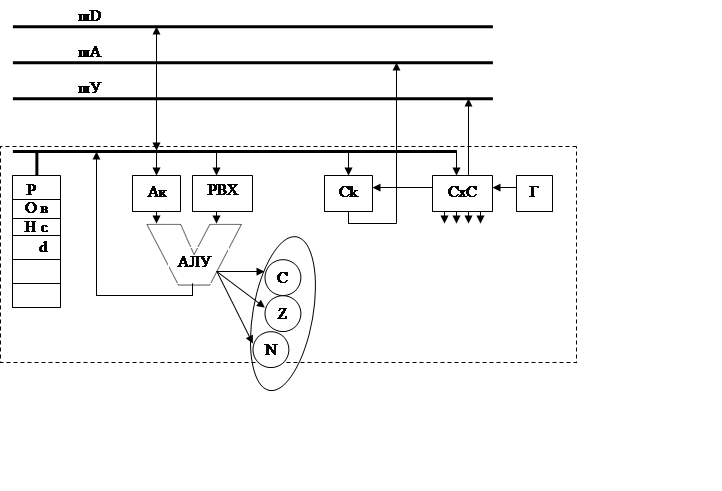

шD – шина данных: поток информации в одном направление:

параметры:

разрядность шины данных: (4, 8, 16, 32 64).

ЗВХ – регистр временного хранения (обычно недоступен для изменений).

РОН – регистр общего назначения:

параметры:

Данный блок характеризуется размером регистра общего назначения:

В RISC машинах 34 – 64.

В CISC машинах 8 – 16.

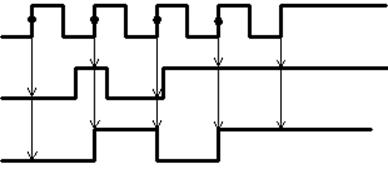

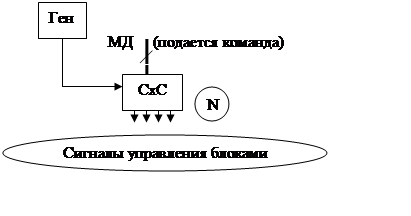

Схема синхронизации:

fт – тактовая частота.

МД – магистраль данных.

Разрядность: определяет структуру вертикального и горизонтального программирования:

Горизонтальное программирование: N – сигналов управления управляет всеми блоками сразу (за 1 такт).

Вертикальное программирование: меньше N – сигналов управления, устройства подключаются последовательно.

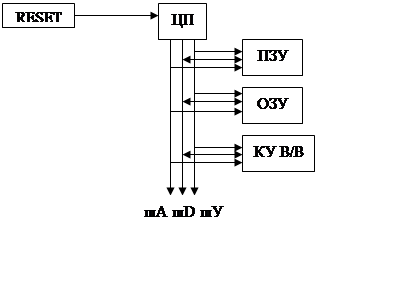

Цикл фон Нейма.

Структура команд.

- Служебные:

Общий сброс системы.

Восстановление системы.

Ожидание.

- Пересылки данных.

- Арифметические и логические.

- Переходов.

- Обработки прерываний.

Команды.

Линейное программирование: команды последовательно расположены: для их организации нужен счетчик команд – Ск.

Разрядность шины адреса определяет разрядность счетчика команд.

Разрядность шины данных может не совпадать с разрядностью других шин.

Обобщенная схема структуры процессора на шинах.

Структура общей шины.

Структура общей шины.

Управляющие данные, коды.

Контроллеры устройств ввода вывода – для обмена между устройствами. (Данные: клавиатуры, сегментов).

Все устройства подключаются к общей шине.

Подключение:

Чтение кода команд.

|

. |

. |

. |

. |

. |

. |

. |

. |

- служебные:

код операции

- пересылка:

|

. |

. |

. |

. |

. |

. |

. |

. |

![]()

![]()

Код информация –

операции источники данных

DEC’овская архитектура - двухшинная.

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

![]()

![]()

![]() Сразу

с двумя регистрами: одновременно.

Сразу

с двумя регистрами: одновременно.

Код источник приемник операции

![]()

010204

код источник приемник

в DEC’овской архитектуре все по 8.

010001

![]() пересылка регистр

р0

пересылка регистр

р0

![]() регистр р1

регистр р1

Суммирование:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.