В состав генератора входят счетчики Divider и Counter_ROM, обеспечивающие перебор адресов ПЗУ Mem_ROM с циклом повторения, позволяющим наблюдать сигналы с помощью светодиодов. Система полностью синхронная и работает с тактовой частотой 25МГц. В ПЗУ Mem_ROM загружаются данные, которые соответствуют сложному периодически повторяющемуся сигналу в соответствии с заданием. Данные с выхода ПЗУ Mem_ROM поступают на выходы Out[7..0], не имеющие физического назначения на выводы используемой микросхемы (Virtual Pin). Логический 0 на выходе led_en разрешает работу светодиодов LED[8..1].

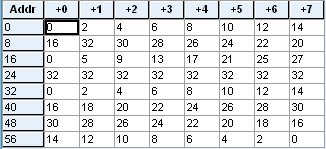

Данные из задания:

Рис 9. Данные, обеспечивающие формирование сигнала заданной формы согласно варианту задания

Выполним компиляцию и проанализируем аппаратурные затраты:

|

Блок проекта |

LC Combinationals |

LC Registers |

F max, МГц |

Время компиляции, сек |

|

Divider |

18 |

18 |

163.03 |

17 |

|

Counter_ROM |

6 |

6 |

||

|

Mem_ROM |

32 |

55 |

Создание интерфейса логического анализатора LAI:

Тестовый модуль был настроен для анализа состояния выходной шины Counter_ROM. Назначение выходных сигналов на тестовые выводы производилось с помощью Pin Planner. Состояние светодиодов LED[3..0] подтвердило правильность работы устройства:

· При подключении Bank_0 видим мигание 2, 3, 4 и 5 разрядов, при этом 5-й разряд мигает реже всех, 4 – в 2 раза чаще и т.д.

· При подключении Bank_1 видим 0 и 1 разряды, их мигание практически не воспринимается глазом.

Аппаратурные затраты для реализации тестовых модулей: отладочные средства: 479 логических элемента, генератор: 72 логических элемента

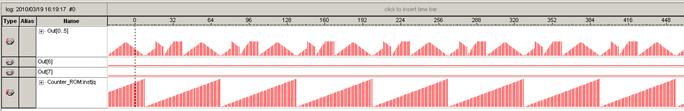

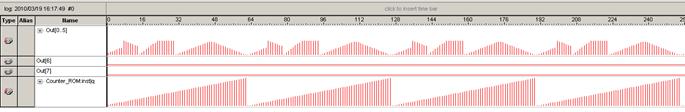

Сравним форму реализованного сигнала с требуемой в задании:

Рис 10. Форма реализованного сигнала вSignalTap II

Видим, что сигнал по форме совпадает с требуемым, что подтверждает работоспособность устройства.

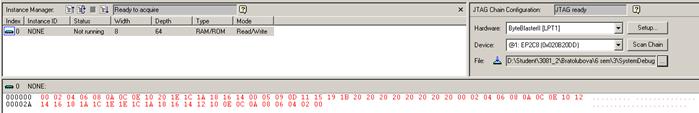

Прочитаем заданные данные с помощью In System Memory Content Editor:

Рис 11. Записанные данные в шестнадцатеричном коде

Видим, что полученные данные соответствуют заданным в файле инициализации памяти.

Изменим данных по нескольким адресам и посмотрим на изменение формы сигнала:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.