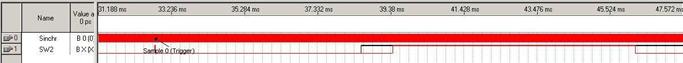

Сравнение двух файлов, наблюдаемых логическим анализатором, с помощью Compare to Waveforms in File:

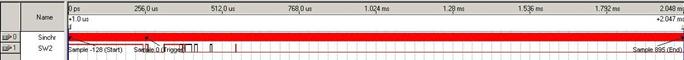

Для анализа минимальной длительности импульсов дребезга зададим максимальную разрешающую способность логического анализатора, выбрав максимальную тактовую частоту записи в кольцевой буфер, и выполним запись сигналов с выхода переключателя.

Устройство PLL увеличивает входную тактовую частоту 25 МГц до значения, близкого к максимальной тактовой частоте.

Рис 2. Схема для анализа минимальной длительности импульсов дребезга

максимальная тактовая частота работы проекта (максимальная тактовая частота записи в кольцевой буфер логического анализатора SignalTapII):145 МГц

Определение длительности процесса переключения и количества импульсов дребезга:

|

0 → 1 |

1 → 0 |

||

|

длительность |

количество импульсов |

длительность |

количество импульсов |

|

127 |

4 |

104 |

3 |

|

106 |

1 |

147 |

6 |

|

0 |

0 |

206 |

4 |

|

0 |

0 |

82 |

3 |

|

269 |

1 |

51 |

3 |

Сравнение двух файлов, наблюдаемых логическим анализатором, с помощью Compare to Waveforms:

Исследование широтно-импульсного модулятора с помощью встроенного логического анализатора SignalTap II и In-System Sourses and Probe Editor.

Цель работы:

Рис 3. Схема для исследования широтно-импульсного модулятора

Исследуемый объект, широтно-импульсный модулятор, состоит из счетчика Counter_PWM, компаратора Compare_PWM и DFF ― триггера. Счетчик работает с тактовой частотой 25МГц. Сигнал с выхода триггера подается на вывод, подключенный к LED1, а комбинаторный вывод для наблюдения при моделировании подключен к виртуальному выходу (Virtual Pin). Данные на компаратор поступают с выхода мультиплексора Mux_Data, который в соответствии с управляющим сигналом Sel коммутирует на свой выход либо внешние данные D[] (сигналы на D[] подаются с переключателей SW[8..1]), либо внутреннюю шину данных DI[].

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.