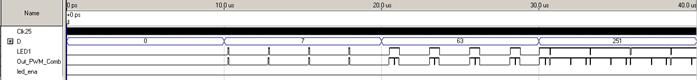

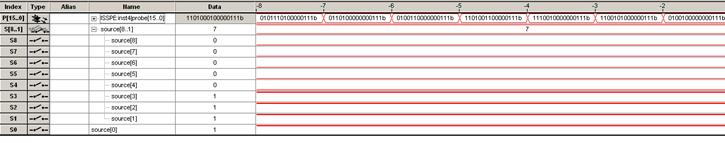

Выполним моделирование. Зададим несколько значений кода D[] (0, маленький код, средний код, код, близкий к максимальному значению):

Рис 4. Моделирование работы ШИМ

Из временной диаграммы видно, что при нулевом входном сигнале сигнала на выходе не будет. Чем больше код, тем шире импульс, и тем ярче будет свечение. На сигнале с выхода комбинаторики присутствуют риски сбоя, в отличие от сигналов с выхода триггера.

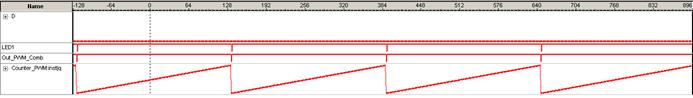

Настроим логический анализатор и запустим программирование. В режиме непрерывной работы убедимся в работоспособности счетчика ШИМ.

Можем наблюдать, что яркость светодиода зависит от кода D, который мы устанавливаем на переключателях.

Рис 5. Работа логического анализатора при разных входных сигналах

Чем больший код мы подаем, тем более широкий импульс мы наблюдаем в логическом анализаторе, и тем ярче светятся светодиоды.

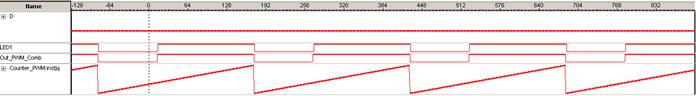

В окне ISSPE установим

внешние данные для работы ШИМ:

В окне ISSPE установим

внешние данные для работы ШИМ:

Рис 6. Окно ISSPE

С помощью source[0] можем регулировать переключение с клавиатуры или с внутренней шины. Если source[0] = 1, то изменение с внутренней шины, если source[0] = 0 – с переключателей.

Запустив режим непрерывного чтения, убеждаемся, что подаваемые на компаратор данные соответствуют положению переключателей SW[].

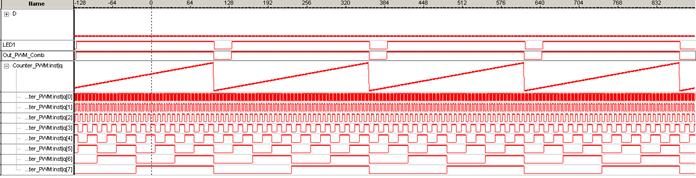

Для управления ШИМ используется код, формируемый генератором линейно растущего, а затем линейно уменьшающегося кода. Генератор реализуется на основе реверсивного счетчика Counter_Triangle.

период формирования выходного сигнала: Т = 2 с

![]() ,

, ![]() , разрядность: 25

, разрядность: 25

Рис 7. Генератор линейно растущего и линейно убывающего сигнала

Счетчик с большим модулем счета досчитывает до максимума, потом переключается, меняется состояние триггера. Вход clk_ena нужен для того, чтобы при переполнении не происходило переключения в 0.

В результате можем наблюдать светодиод, который загорается и гаснет за период, равный 2 секундам.

Исследование и отладка генератора сигналов сложной формы средствами системной отладки Quartus II.

Цель работы:

функций встраиваемого логического анализатора SignalTap II пакета Quartus II, базовых функций интерфейса логического анализатора LAI, базовых функций редактора памяти в системе ISMCE;

Рис 8. Генератор сигналов сложной формы на основе ПЗУ

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.