Белорусский государственный университет транспорта

Электротехнический факультет

Кафедра «МТиУС»

Приложение В

К курсовой работе по дисциплине

«Технические средства микропроцессорных систем»

"Проектирование специализированного микроконтроллера"

Выполнили Проверил

студенты группы ЭМ-51 ассистент

Чаплюк Д.А. и Конопляник П.С. Кузьмич М.С.

Гомель 2007г.

ПРИЛОЖЕНИЕ В

Структура файлов тестовых воздействий:

► test_add_1024.vhd

► test_div_1024.vhd

► test_gcd.vhd

► test_gen_n.vhd

► test_mod_mul_1024.vhd

► test_mul_1024.vhd

► test_mod_exp_1024.vhd

► test_rng.vhd

► test_prime.vhd

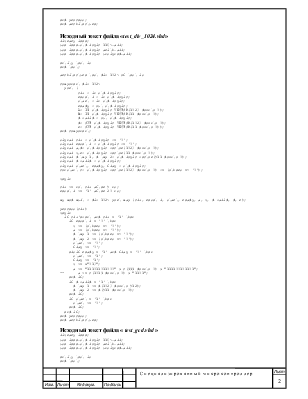

Исходный текст файла «test_add_1024.vhd»

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity test is

end test;

architecture test_add_sub of test is

component add_sub_1024

port (

clk : in std_logic;

reset_l : in std_logic;

start : in std_logic;

ready : out std_logic;

ADD: IN std_logic;

A: IN std_logic_VECTOR(1023 downto 0);

B: IN std_logic_VECTOR(1023 downto 0);

C_IN: IN std_logic;

C_OUT: OUT std_logic;

s_valid : out std_logic;

S: OUT std_logic_VECTOR(1023 downto 0));

end component;

signal clk : std_logic := '0';

signal reset_l : std_logic := '0';

signal a,b,s: std_logic_vector(1023 downto 0);

signal c_in : std_logic;

signal c_out : std_logic;

signal s_valid : std_logic;

signal start, ready : std_logic;

constant c: std_logic_vector(1023 downto 0) := (others => '1');

begin

clk <= not clk after 5 ns;

reset_l <= '1' after 20 ns;

my_add_sub : add_sub_1024 port map (clk, reset_l, start, ready, '1', a, b, c_in, c_out, s_valid, s);

process(clk)

begin

if clk'event and clk = '1' then

if reset_l = '0' then

b <= (others => '0');

a <= (others => '0');

c_in <= '0';

elsif ready = '1' then

start <= '1';

a <= a + 300000000;

b <= b + c;

c_in <= '0';

end if;

if start = '1' then

start <= '0';

end if;

end if;

end process;

end architecture;

Исходный текст файла «test_div_1024.vhd»

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity test is

end test;

architecture test_div_1024 of test is

component div_1024

port (

clk : in std_logic;

reset_l : in std_logic;

start : in std_logic;

ready : out std_logic;

A: IN std_logic_VECTOR(1023 downto 0);

B: IN std_logic_VECTOR(11 downto 0);

d_valid : out std_logic;

d: OUT std_logic_VECTOR(1023 downto 0);

r: OUT std_logic_VECTOR(11 downto 0));

end component;

signal clk : std_logic := '0';

signal reset_l : std_logic := '0';

signal a,d: std_logic_vector(1023 downto 0);

signal b,r: std_logic_vector(11 downto 0);

signal d_tmp_1, d_tmp_2: std_logic_vector(511 downto 0);

signal d_valid : std_logic;

signal start, ready, flag : std_logic;

constant c: std_logic_vector(1023 downto 0) := (others => '0');

begin

clk <= not clk after 5 ns;

reset_l <= '1' after 20 ns;

my_mod_mult : div_1024 port map (clk, reset_l, start, ready, a, b, d_valid, d, r);

process(clk)

begin

if clk'event and clk = '1' then

if reset_l = '0' then

b <= (others => '0');

a <= (others => '0');

d_tmp_1 <= (others => '0');

d_tmp_2 <= (others => '0');

start <= '0';

flag <= '0';

elsif ready = '1' and flag = '0' then

start <= '1';

flag <= '1';

b <= x"013";

a <= "111011011000" & c(999 downto 0) & "111100101101";

-- a <= c(1019 downto 0) & "1101";

end if;

if d_valid = '1' then

d_tmp_1 <= d(1023 downto 512);

d_tmp_2 <= d(511 downto 0);

end if;

if start = '1' then

start <= '0';

end if;

end if;

end process;

end architecture;

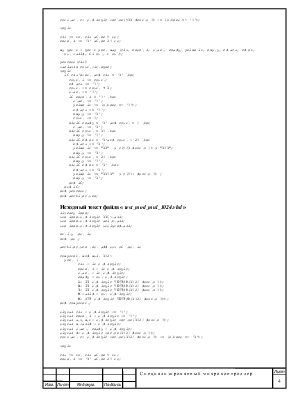

Исходный текст файла « test_gcd.vhd »

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity test is

end test;

architecture test_gcd of test is

component gcd

port (

clk : in std_logic;

reset_l : in std_logic;

start : in std_logic;

ready : out std_logic;

A: IN std_logic_VECTOR(1023 downto 0);

out_valid : out std_logic;

d: OUT std_logic_VECTOR(1023 downto 0);

e: OUT std_logic_VECTOR(1023 downto 0));

end component;

signal clk : std_logic := '0';

signal reset_l : std_logic := '0';

signal a,d,e: std_logic_vector(1023 downto 0);

signal out_valid : std_logic;

signal start, ready : std_logic;

signal tmp: std_logic_vector(511 downto 0);

constant c: std_logic_vector(511 downto 0) := (others => '1');

begin

clk <= not clk after 5 ns;

reset_l <= '1' after 20 ns;

my_gcd : gcd port map (clk, reset_l, start, ready, a, out_valid, d,e);

process(clk)

begin

if clk'event and clk = '1' then

if reset_l = '0' then

a <= (others => '0');

tmp <= x"8" & x"0000" & c(491 downto 0);

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.