Архітектура EPIC - Explicitly Parallel

Instruction Computing і процесор Intel Itanium.

Архітектура EPIC представляє собою результат науково-дослідної розробки, що представляє

собою швидше принцип обробки інформації, ніж архітектуру конкретного процесора. В архітектурі поєднуються багато досить

різнотипних технологічних рішень, які в результаті поєднання дають значне підвищення

швидкості обробки й рішення деяких проблем трансляції програм.

Архітектура EPIC (базові принципи) були розроблені в університеті Іллінойсу, проект мав назву Impact. На початку 1990-х років були закладені теоретичні основи самої архітектури, потім були розпочаті роботи в рамках створення інструментальних засобів для процесора EPIC. Проект по створенню інструментальних засобів відомий під назвою Trimaran. Архітектура EPIC має такі основні особливості:

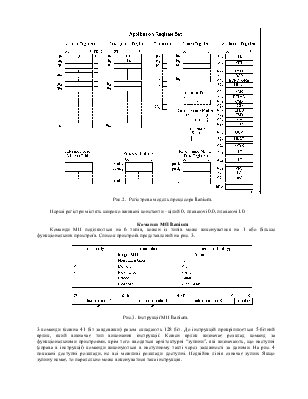

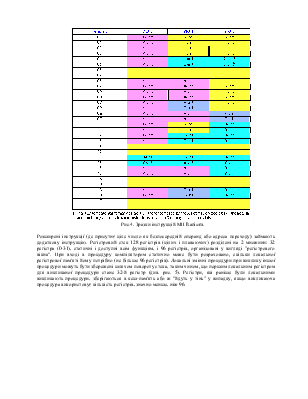

• підтримка явно виділеного компілятором паралелізму. Формат команд має багато спільного з архітектурою з довгим командним словом - паралелізм так само явно виділено. Однак, якщо довге командне слово має зазвичай чітко задану ширину, в процесорі EPIC існує деяка кількість зразків довгих команд, в яких функціональним пристроям процесора явно призначена операція. Крім того, ряд пристроїв може зіставляти інструкції з різних тактів виконання, тобто інструкція явно виконується за 1-2 такти, в цьому випадку у зразку інструкції явно специфіковані між командами є слот затримки (фактично "межа" між командами, що виконуються в різних тактах). До кожної довгої команді (128 біт) додається невеликий (3-5 бітний) ярлик, який специфікує формат команди.

• наявність великої регістрового файлу

• наявність предикатних регістрів, подібно архітектурі PowerPC. Предикатні регістри дозволяють позбавиться від відомої проблеми з неподільним ресурсом регістра прапорців більшості процесорів, що підтримують скалярний паралелізм - програмна конвеєризація циклів, що містять умовні переходи, практично неможлива. Множинний предикатний регістр прапорців дозволяє позбавиться від паразитних зв'язків з управління через регістр прапорців.

• спекулятивне завантаження даних, дозволяє уникнути простою конвеєра при завантаженні даних з оперативної пам'яті.

• підтримка предикатної-виконуваних команд, яка дозволяє: 1) уникнути лишніх інструкцій розгалуження, якщо кількість команд в гілках умовного оператора невелика, 2) зменшити навантаження на пристрій передбачення переходів.

• апаратна підтримка програмної конвеєризації за допомогою механізму перейменування регістрів.

• використання стеку регістрів (і регістрові вікна).

• Для передбачення інструкцій використовується підтримка компілятора.

• Є підтримка програмної конвеєризації (метод складання розділу команд "по модулю") циклів, коли на кожній ітерації імена регістрів зсуваються і кожна нова ітерація оперує вже з новим набором регістрів.

• Введена підтримка інструкцій циклічного виконання команд без втрат часу на інструкції циклічного виконання.

Також в архітектурі EPIC є підтримка спекулятивне виконання команд і завантаження даних.

• Спекулятивне виконання команд. Більшість команд завантаження даних з пам'яті виконується тривалий час. Виконання команди за 1-2 такти можливо тільки в тому випадку, якщо значення міститься в кеш-пам'яті другого рівня. Час дещо збільшується, якщо значення знаходиться в кеш-пам'яті другого рівня. У разі читання же даних з мікросхем динамічної пам'яті навіть при попаданні на активну сторінку відбувається значна затримка при завантаженні, а при зміні сторінки затримка має астрономічну величину, причому конвеєр швидко блокується, так команд, які можна виконати без порушення залежності за даними, зазвичай виявляється вкрай мало.

При спекулятивному виконанні використовується винесення команд завантаження перед інструкціями, що використовують ці дані, в основному вище за інструкції умовного переходу. При досягненні потоком команд місця, де необхідно використовувати завантажені дані, вставляється інструкція, що перевіряє чи не відбулося виключення в процесі завантаження (наприклад, якась інструкція справила запис за цією адресою), якщо виключення відбулося, то викликається спеціально написаний відновлювальний код, який просто перезавантажує значення в регістр.

При спекулятивних операціях за даними оптимізується часто зустрічається ділянку в багатьох програмах. Фрагмент програми:

int * p, * t;

int a, b;

...

* P = b;

a = * t;

У випадку, якщо компілятор не має достатньо інформації для проведення аналізу потоку даних, він не може визначити, перекриваються області пам'яті, адресовані вказівниками чи ні. У цьому випадку кожен раз значення треба перезавантажувати, але, мало того, інструкції завантаження не можна впорядкувати. Для отримання можливості переупорядочивания цих інструкцій використовується спекуляція за даними. Інструкція завантаження переноситься наверх, при цьому, якщо зроблений запис, що зачіпає завантажувати вміст, то проводиться виклик коду відновлення, перезавантажуємо значення.

Архітектура EPIC є чудовим прикладом впровадження теоретичних розробок у виробництво, про що красномовно свідчить ситуація на ринку апаратного забезпечення.

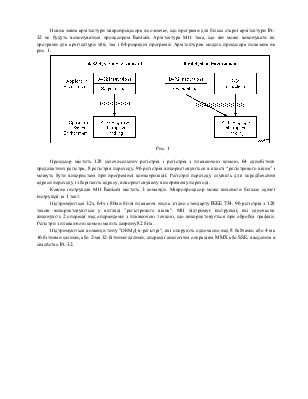

Архітектура процесора Itanium. Загальні відомості

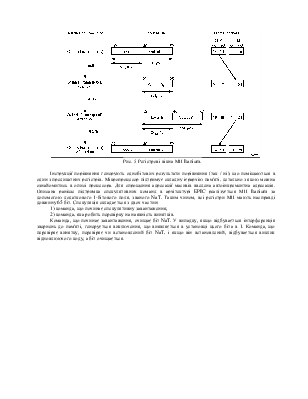

Першим зразком 64-розрядного процесора Intel є картридж розміром приблизно 10х6 см, який включає в себе процесор, кеш-пам'ять третього рівня ємністю 2 або 4 Мбайт і радіатор. Картридж монтується в роз'єм типу Slot і має 418 виводів. Процесор має трирівневу ієрархію надоперативної пам'яті. Якщо кеш-пам'ять першого і другого рівнів інтегрована на кристалі процесора, то мікросхеми кеш-пам'яті третього рівня розташовані на самій платі картриджа. На реалізацію процесора з дотриманням проектних норм 0,18 мкм було потрібно близько 320 млн. транзисторів, з яких тільки 25 млн. відводилось на реалізацію самого ядра, а решта - на кеш-пам'ять. Найбільший модуль процесора - це блок обчислень з плаваючою комою, він займає близько 10% площі кристала. Продуктивність Itanium становить до 6,4 млрд. операцій з плаваючою комою в секунду. Завдяки архітектурі EPIC і 15 виконавчим пристроям процесор може виконувати до 20 операцій одночасно. При цьому він може безпосередньо адресувати до 16 Тбайт пам'яті при пропускної здатності до 2,1 Гбайт / с. У процесорі реалізована підтримка всіх розширень Intel (технологій MMX, SIMD та симетричною мультипроцесорної обробки), за винятком SSE2.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.