Одна з найцікавіших деталей в плані розміщення вузлів процесора - це система синхронізації роботи вузлів. Одночасна передача тактових імпульсів при великій площі процесора представляє складну задачу для розробників, оскільки затримки в поширенні імпульсів тактового генератора можуть викликати розсинхронізацію вузлів. Для цієї мети по всій площі кристала розмістили велику кількість точок розповсюдження тактових імпульсів.

Архітектура Itanium включає такі унікальні засоби підвищення надійності, як система розширеного самоконтролю EMCA (Enhanced Machine Check Architecture), що забезпечує виявлення, корекцію і протоколювання помилок, а також підтримку обробки коду ECC (Error Correcting Code) та контролю парності.

Для двох-і чотирипроцесорних систем Intel випустила спеціальний набір мікросхем Intel 460GX, які можуть включатися каскадно, збільшуючи число одночасно використовуваних процесорів. Оскільки конфігурація таких систем спочатку передбачає обсяги оперативної пам'яті в кілька гігабайт, то в системах Itanium застосовуються порівняно недорогі мікросхеми пам'яті типу SDRAM. При цьому для збільшення продуктивності, використовуються такі методи, як буферизування, чергування і поділ пам'яті на кілька банків. Набір мікросхем реально підтримує роботу з 64 Гбайт пам'яті при максимальної пропускної здатності 4,2 Гбайт / с, хоча 64-розрядна адресація пам'яті теоретично дозволяє звертатися до набагато більшій кількості адрес.

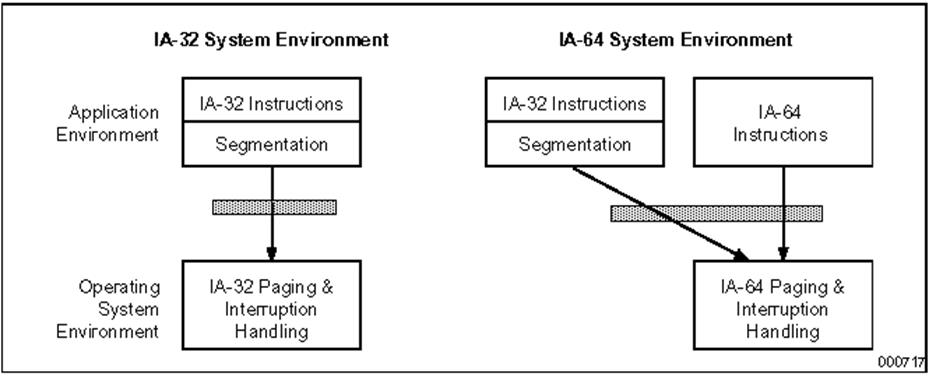

Повна зміна архітектури мікропроцесора не означає, що програми для більш старої архітектури IA-32 не будуть виконуватися процесором Itanium. Архітектура МП така, що він може виконувати як програми для архітектури х86, так і 64-розрядні програми. Архітектурна модель процесора показана на рис. 1.

Рис. 1

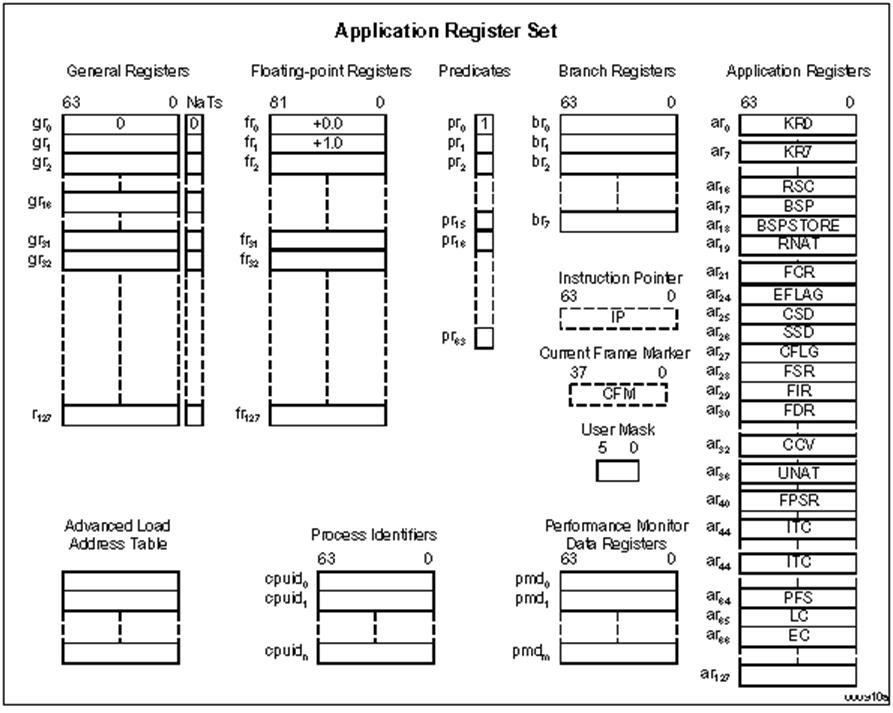

Процесор містить 128 цілочисельних регістрів і регістрів з плаваючою комою, 64 однобітних предикатних регістра, 8 регістрів переходу. 96 регістрів використовуються в якості “регістрового вікна" і можуть бути використані при програмної конвеєризації. Регістри переходу служать для передбачення адреси переходу і зберігають адресу, використовувану в непрямому переході.

Кожна інструкція МП Itanium містить 3 команди. Мікропроцесор може виконати більше однієї інструкції за 1 такт.

Підтримуються 32х, 64х і 80ми бітні плаваючі числа згідно стандарту IEEE 754. 96 регістрів з 128 також використовуються у вигляді "регістрового вікна". МП підтримує інструкції, які одночасно виконують 2 операції над операндами з плаваючою точкою, що використовується при обробці графіки. Регістри з плаваючою комою мають ширину 82 біта.

Підтримуються команди типу "ОКМД-в-регістрі", які оперують одночасно над 8 байтами, або 4-ма 16-бітними цілими, або 2-мя 32-бітними цілими, операції аналогічні операціям MMX або SSE, введеним в сімейство IA-32.

Рис.2. Регістрова модель процесора Itanium.

Перші регістри містять широко вживані константи - цілий 0, плаваючі 0.0, плаваючі1.0.

КомандиМПItanium

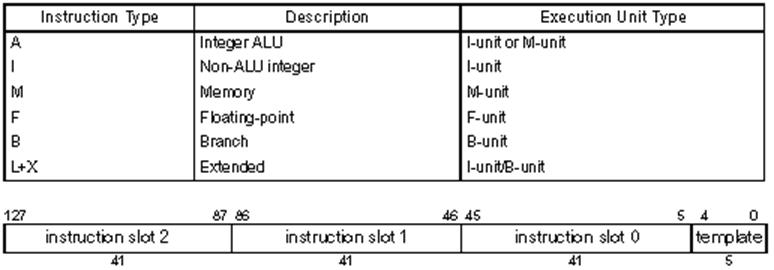

Команди МП поділяються на 6 типів, кожен із типів може виконуватися на 1 або більше функціональних пристроїв. Список пристроїв представлений на рис. 3.

Рис.3. Інструкції МП Itanium.

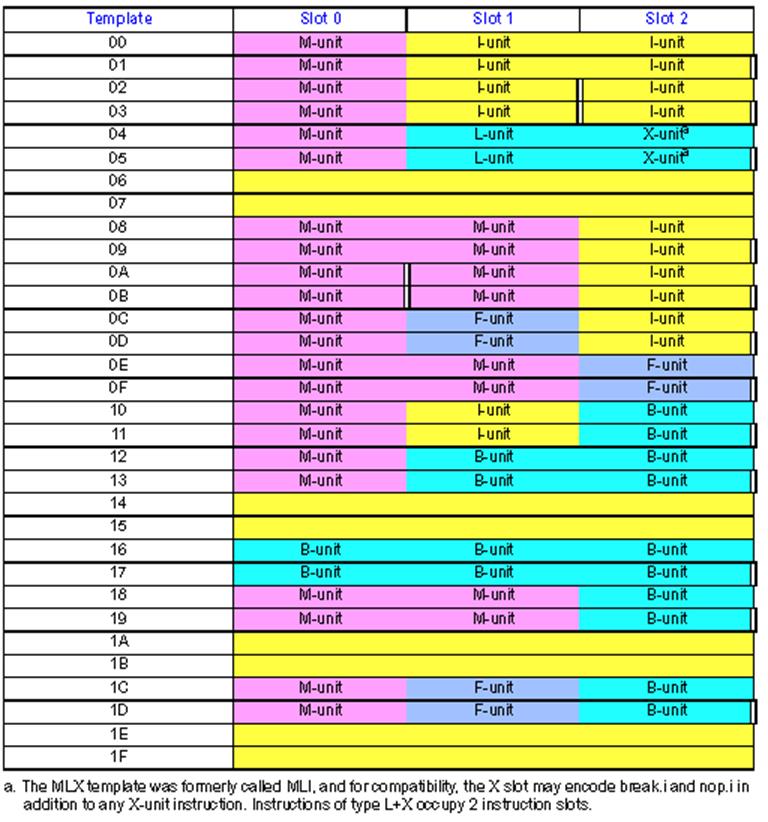

3 команди (кожна 41 біт завдовжки) разом складають 128 біт. До інструкцій прикріплюється 5-бітний ярлик, який визначає тип виконання інструкції. Кожен ярлик визначає розклад команд за функціональними пристроями, крім того вводяться архітектурні "зупини", які визначають, що наступні (справа в інструкції) команди виконуються в наступному такті через залежності за даними. На рис. 4 показані доступні розклади, не всі можливі розклади доступні. Подвійна лінія означає зупин. Якщо зупину немає, то паралельно може виконуватися така інструкція.

Рис.4. Зразки інструкцій МП Itanium.

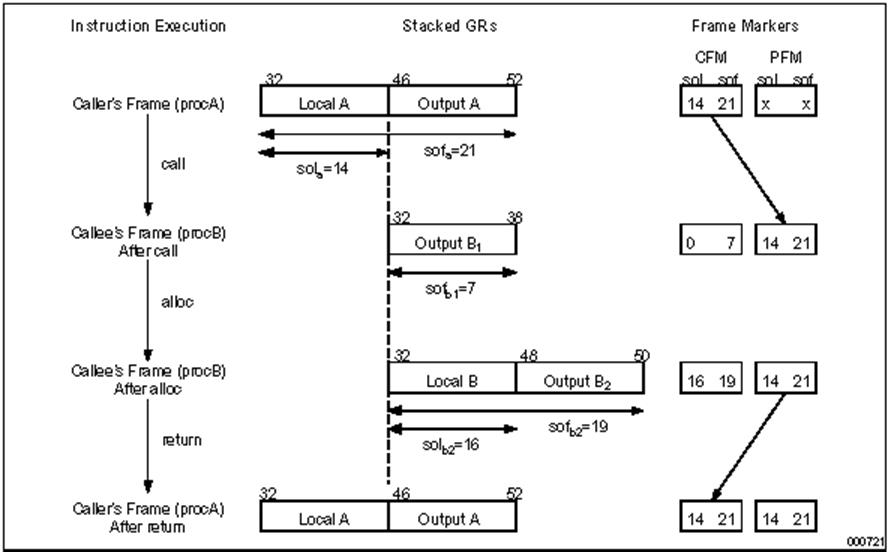

Розширені інструкції (де присутнє ціле число як безпосередній операнд або адреса переходу) займають додаткову інструкцію. Регістровий стек 128 регістрів (цілих і плаваючих) розділені на 2 множини: 32 регістра (0-31), статичні і доступні всім функціям, і 96 регістрів, організовані у вигляді "регістрового

вікна". При вході в процедуру компілятором статично може бути розраховано, скільки локальної регістрової пам'яті йому потрібно (не більше 96 регістрів). Локальні змінні процедури при виклику іншої процедури можуть бути збережені шляхом повороту стека, таким чином, що першим локальним регістром для викликаної процедури стане 32-й регістр (див. рис. 5). Регістри, які раніше були локальними викликають процедури,

зберігаються в кеш-пам'ять або ж "йдуть у тінь" у випадку, якщо викликаюча процедура використовує кількість регістрів, значно менше, ніж 96.

Рис. 5 Регістрові вікна МП Itanium.

Інструкції порівняння генерують однобітових результати порівняння (так / ні), що поміщаються в один з предикатних регістрів. Мікропроцесор підтримує складну ієрархію пам'яті, детально з якою можна ознайомитись в описі процесора. Для спрощення адресації масивів введена автоінкрементна адресація. Описана раніше підтримка спекулятивних команд в архітектурі EPIC реалізується МП Itanium за допомогою додаткового 1-бітового поля, званого NaT. Таким чином, всі регістри МП мають насправді довжину 65 біт. Спекуляція складається з двох частин:

1) команда, що починає спекулятивну завантаження;

2) команда, яка робить перевірку на наявність винятків.

Команда, що починає завантаження, очищає біт NaT. У випадку, якщо відбувається інтерференція звернень до пам'яті, генерується виключення, що виявляється в установці цього біта в 1. Команда, що перевіряє винятку, перевіряє чи встановлений біт NaT, і якщо він встановлений, відбувається виклик відновлюючого коду, а біт очищається.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.