Совмещенная ИС — это микросхема, у которой активные элементы выполнены в приповерхностном слое полупроводниковой подложки (как у полупроводниковой ИС), а пассивные элементы нанесены в виде пленок на предварительно изолированную поверхность той же подложки (как у пленочных ИС).

Во всех типах ИС соединения элементов осуществляются с помощью тонких металлических полосок, напыленных или нанесенных на поверхность подложки и контактирующих в нужных местах с соединяемыми элементами. Процесс нанесения этих соединительных полосок называется металлизацией, а сам рисунок соединений — металлической разводкой.

Достоинствами полупроводниковых ИС являются:

· возможность широкой автоматизации производства и высокая плотность упаковки элементов, что обуславливает низкую стоимость этих ИС;

· высокое качество активных элементов.

Недостатками полупроводниковых ИС являются:

· относительно низкие параметры пассивных элементов;

· наличие заметных гальванических и емкостных связей между элементами;

· сложность и дороговизна технологического оборудования.

К достоинствам совмещенных ИС можно отнести высокие номиналы и высокую стабильность сопротивлений и емкостей, а к недостаткам — более сложную технологию и связанную с этим высокую стоимость.

Достоинствами ГИС являются относительная простота и доступность технологии, высокие параметры пассивных и активных элементов и существенно более низкая стоимость по сравнению с полупроводниковыми ИС при мелкосерийном изготовлении.

Недостатки ГИС — относительно низкая плотность упаковки элементов, большой процент ручных операций.

По функциональному назначению микросхемы подразделяют на цифровые (логические ), аналоговые ( линейные ) и СВЧ — ИС.

По применяемости в аппаратуре микросхемы делятся на изделия широкого применения и частного применения (специализированные микросхемы, рассчитанные на использование в отдельной конкретной аппаратуре и выпускаемые поэтому относительно малым тиражом).

В настоящее время наиболее широкое распространение получили средние и большие цифровые и аналоговые ИС широкого применения, поэтому в этой работе рассматриваются именно такие микросхемы.

Существуют два конкурирующих между собой метода построения полупроводниковых ИС :

— на базе биполярных транзисторов ( БТ — ИС );

— на базе МДП транзисторов ( МДП — ИС ).

Для сравнительного анализа структуры БТ — ИС и МДП — ИС рассмотрим особенности структуры элементов, входящих в состав этих ИС.

1.3. Элементы полупроводниковых ИС

Интегральные элементы имеют ряд особенностей по сравнению с их дискретными аналогами:

· они имеют электрическую связь с общей подложкой, а иногда и друг с другом;

· все элементы ИС получаются в едином технологическом цикле (групповая технология ).

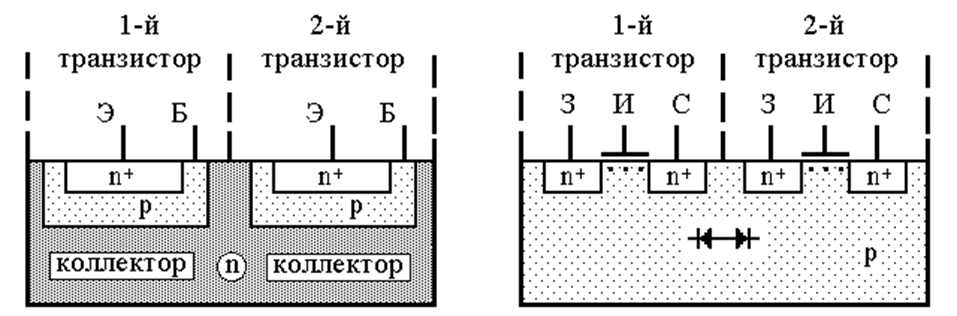

Первая особенность приводит к тому, что эквивалентные схемы элементов ИС несколько отличаются от эквивалентных схем дискретных аналогов. Кроме того, в БТ — ИС она приводит к необходимости применения специальных мер для изоляции элементов друг от друга, поскольку они оказываются принудительно связанными через подложку. Например, транзисторы имеют общий коллектор и могут быть включены только по схеме с общим коллектором, что не позволяет построить все необходимое разнообразие схем ( рис. 1).

Рис.1. Внутренняя связь элементов Рис.2 . Отсутствие связи между

БТ-ИС в отсутствии изоляции элементами МДП-ИС

В МДП — ИС истоки и стоки смежных транзисторов разделены встречно включенными p-n переходами ( рис. 2 ), поэтому гальваническая связь между элементами осуществляется только обратными токами переходов. Ввиду ничтожной малости этих токов в кремниевых переходах такой связью можно пренебречь, поэтому в МДП — ИС специальной изоляции элементов не требуется, что является одним из преимуществ МДП — ИС.

1.3.1. Методы изоляции элементов БТ — ИС

Все известные методы изоляции элементов БТ — ИС сводятся к двум основным :

· изоляции с помощью закрытого p-n перехода по аналогии с самоизоляцией элементов МДП — ИС ( диодная изоляция );

· изоляция с помощью диэлектрика.

Достоинствами диодной изоляции являются меньший на 3 — 5 порядков ток утечки по сравнению с обратными токами перехода и меньшие на порядок паразитные емкости. Недостатком ее является более сложная технология, приводящая к более высокой стоимости ИС.

Методы получения изолирующих переходов зависят от технологии изготовления ИС. В ранее применяемой чисто планарной технологии эти переходы получались методами тройной диффузии и встречной диффузии, которые обладают рядом серьезных недостатков.

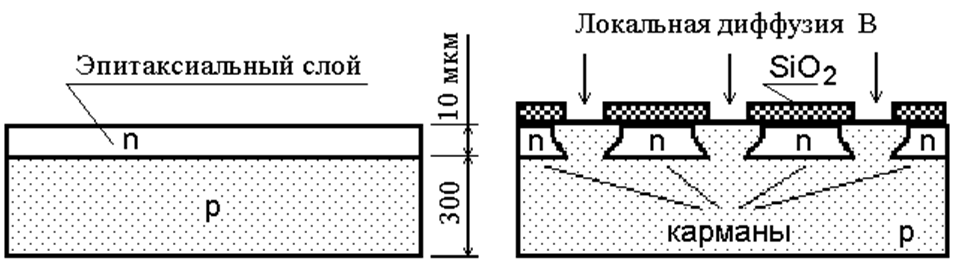

В настоящее время для изготовления БТ—ИС используется более прогрессивная эпитаксиально-планарная технология, при которой вместо монолитной пластины n-типа используется тонкий эпитаксиальный n-слой ( толщиной 1-10 мкм ), выращенный на подложке p-типа (рис.3,а ).

На поверхности n-слоя методами фотолитографии формируется маска для проведения диффузии изолирующей p-области ( рис.3,б ). После диффузии до встречи с p-подложкой в n-слое формируются “островки” n-типа, окруженные снизу и с боков полупроводником p-типа. Эти “островки” называют карманами, в которых формируются интегральные элементы.

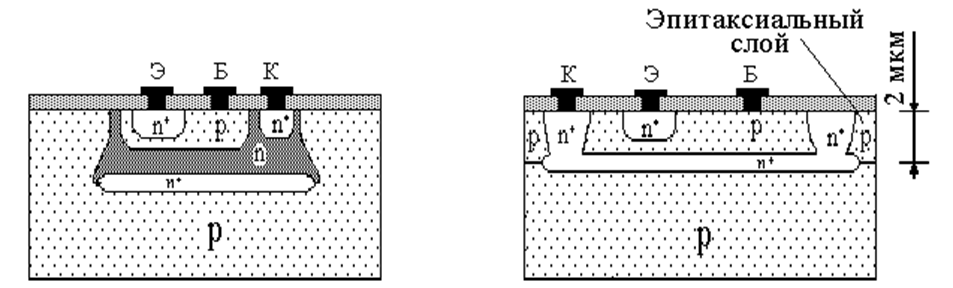

Применяют также более сложные карманы, содержащие на дне скрытый n+ слой, который способствует уменьшению сопротивления коллектора интегрального транзистора и частично экранирует элемент от влияния подложки ( рис.4 ).

а) б)

Рис.3. Основной способ изоляции элементов при эпитаксиально-планарной технологии БТ-ИС

Рис.4. Изолированный карман Рис.5. Изоляция элементов

со скрытым n+ слоем коллекторной диффузией

Скрытые слои получают локальной диффузией, которая проводится в пластину p-типа до наращивания эпитаксиального слоя. При проведении эпитаксии и последующих операций диффузии примеси скрытого слоя диффундируют в эпитаксиальный n-слой, в результате чего скрытый слой частично располагается в эпитаксиальном слое, приподнимая дно кармана.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.