СуперЭВМ представляют собой самый мощный класс компьютеров. В большинстве суперЭВМ используются 64-разрядные слова, над которыми выполняются операции с плавающей запятой от 10·106 до 10·109 Флопс. Они используются для решения научных и инженерных задач в тех случаях, когда целесообразно применение векторной обработки на основе архитектур ОКМД и МКМД. Организация традиционных суперЭВМ, таких как CRAY и NEC, определяется применением быстродействующих электронных схем, скомпонованных с высокой плотностью для уменьшения задержек прохождения сигналов.

Следует отметить, что в приведенном широком классе ММПС особое место занимают проблемно-ориентированные ММПС для цифровой обработки сигналов (ЦОС). Этот класс МППС решает широкий круг задач, связанных с распознаванием образов, моделированием нейронов мозга, гидро- и радиолокационных задач, сейсмографии, радиофизики и т.п.

Главным архитектурным различием между традиционным ЭВМ, предназначенными для обработки коммерческой информации, является что, что мини-, супер-мини-, универсальные и мегауниверсальные ЭВМ имеют, главным образом, скалярную архитектуру, а ЭВМ для научных расчетов (супер, мини- суперЭВМ, матричные процессоры и ММПС ЦОС) – векторную.

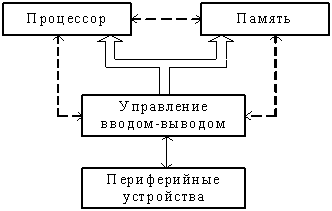

Скалярная ЭВМ (рис. 17.1) имеет традиционную фон-неймановскую (т.е. ОКОД) организацию, для которой характерно наличие одной шины данных и последовательное выполнение обработки элементов одиночных данных.

Рисунок 17.1 - Структура скалярной ЭВМ

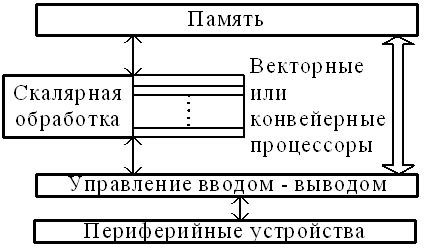

Векторная ЭВМ (см. рис. 17.2) имеет в своем составе раздельные векторные процессоры или конвейеры и одна команда выполняется в ней над несколькими элементами данных (векторами).

Рисунок 17.2 - Структура векторной ЭВМ

Векторные архитектуры - это, в основном, архитектуры типа ОКМД, но некоторые из них относятся к классу МКМД. Векторная обработка увеличивает производительность процессорных элементов, но требует наличия полного параллелизма в ходе обработки задач.

Параллелизм в ММПС может быть использован для повышения их производительности на нескольких уровнях:

- между работами или фазами работы;

- между частями программы или в пределах циклов;

- между элементами векторной операции;

- на уровне арифметических и логических схем.

Первые две категории образуют область, которая может быть названа классом параллельных ММПС, а третья и четвертая являются более «тонкой» формой параллелизма, которая иногда используется в блоках последовательной обработки и часто реализуется с помощью конвейерных процессоров.

Ниже приведены основные архитектурные формы параллельных ММПС, которые используются или создаются в настоящее время.

Архитектура с потоком управления. Суть ее заключается в том, что отдельный управляющий процессор служит для посылки команд множеству процессорных элементов, каждый из которых состоит из процессора и связанной с ним памяти.

Архитектура с потоком данных. Она децентрализована в очень высокой степени и выполняемые ею параллельные команды посылаются вместе с данными в другие (и очень многие) одинаковые процессоры.

Архитектура с управлением по запросам. Она разбивает решаемые задачи на менее сложные подзадачи и результаты их решения снова объединяются для формирования окончательного результата. Команда, которую следует выполнять, определяется, когда ее результат оказывается нужным для другой активной команды.

Архитектура с управлением наборами условий. Работает аналогично предыдущей архитектуре. Типичное применение такой структуры – распознавание изображений с использованием клеточных матриц процессорных элементов.

Архитектура ЭВМ с общей памятью. В ней используется та или иная система межсоединений для объединения процессоров с памятью. Системы межсоединений могут быть конструктивно оформлены в виде шин, колец, кубов, кэшей.

Архитектура с параллельными процессорами. Здесь используется высокая степень параллелизма, которая допускает независимое выполнение нескольких процессов на нескольких процессорах. Для этого класса ММПС широко используемой формой структур параллельной обработки являются гиперкубы, или двоичные n-кубы, в которых между процессорами имеют место двухпунктовые связи для передачи информации между ними (в 16-вершинном кубе каждый процессорный элемент ММПС соединен с четырьмя соседними).

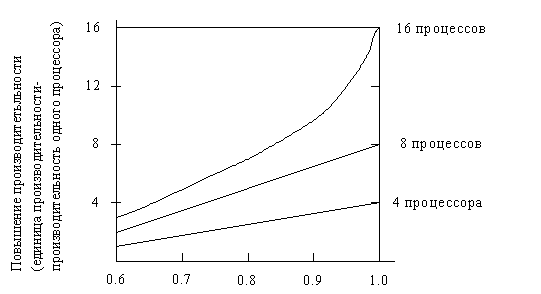

Необходимо отметить, что повышение производительности ММПС, которое может быть достигнуто за счет параллельной обработки, зависит от доли вычислений, которые могут выполняться параллельно. На рис. 17.3 иллюстрируется повышение производительности, которое может быть достигнуто при использовании различного количества процессоров, работающих параллельно, по сравнению с долей Р вычислений, которые могут выполняться параллельно.

Рисунок 17.3 - Зависимость производительности параллельных процессов от доли вычислений Р, выполняемых параллельно

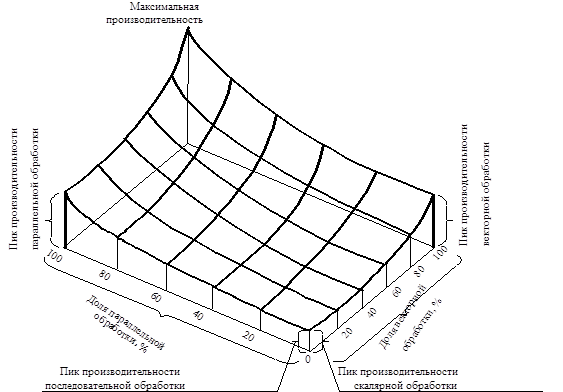

На рис. 17.4 приведено соотношение между возможностями ММПС по выполнению векторной, параллельной и скалярной обработки информации. Увеличение производительности ММПС, которое достигается за счет использования векторной и параллельной обработки, является весьма существенным, поэтому скорость реализации алгоритмов, в которых заложены обе указанные формы параллелизма, возрастает.

Мультимикропроцессорные системы, которые являются параллельными ЭВМ, строятся из большого числа процессоров, располагающих собственной памятью, и используют широкий спектр связей между процессорами для обмена. Топологии этих МПС могут быть организованы в соответствии со следующими схемами:

- древовидные сети;

- шины;

- конвейеры;

- процессоры БПФ;

- сети перекрестного обмена;

- гиперкубы;

- сетки (решетки) с одним, двумя, тремя или большим числом измерений;

- кольца;

- цилиндры;

- тороиды;

- пирамидальные сети.

Рисунок 17.4 - Взаимосвязь между векторной, параллельной и скалярной производительностью ММПС

Перечисленные выше структуры сопоставляются по следующим характеристикам: легкость реализации системы на основе существующих устройств, сложность соединительной сети, наличие предпосылок для расширения структуры, сопоставление используемого алгоритма и структуры системы. На рис. 17.5 приведен набор топологических решений для реализации тех или иных алгоритмов.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.