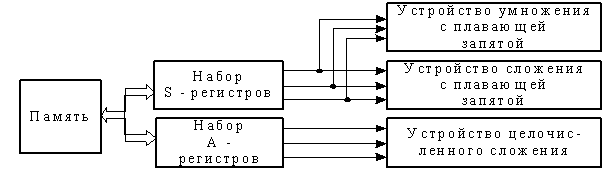

Архитектура скалярной суперЭВМ относится к типу SISD – архитектур, подобна скалярной архитектуре суперЭВМ CRAY-1 и приведена на рис. 17.7.

В данной архитектуре предусмотрено три функциональных устройства (устройства сложения и умножения с плавающей запятой и устройство целочисленного сложения), а также два набора регистров (S и А). Такая архитектура позволяет достичь высокой производительности за счет того, что здесь максимальная скорость выдачи команд – одна команда в такт.

Рисунок 17.7 - Структура скалярной суперЭВМ

Набор регистров А используется, главным образом, для хранения адресов и для адресных вычислений (например, для вычисления индексов), а набор регистров S – для хранения данных и результатов при выполнении соответствующих команд.

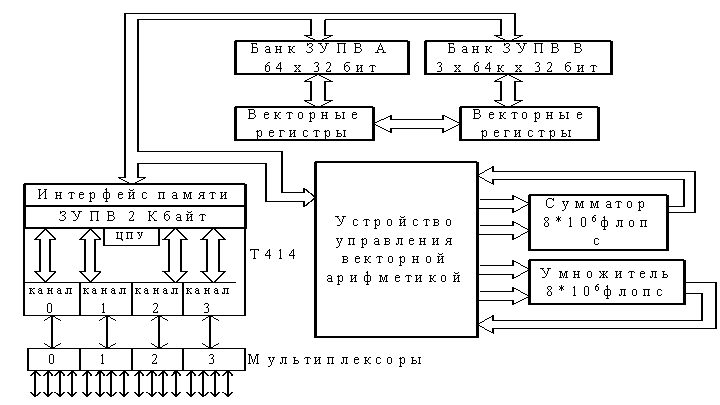

Однородная векторная суперЭВМ серии Т фирмы FPS (Floating Point Systems) была выпущена в 1986 году и превышала производительность всех известных в тот период суперЭВМ. Самая мощная модель серии Т-140000 имеет 16384 узла, каждый из которых содержит транспьютер Т414 и 64-разрядный векторный процессор с плавающей запятой с производительностью 64*106 Флопс, а производительность машины в целом составляет 262*109 Флопс; емкость памяти достигает 16 Гбайт. Программное обеспечение ЭВМ серии Т представляет собой язык параллельной обработки ОККАМ. Каждый узел, конструктивно оформленный в виде одной печатной платы, содержит (рис. 17.8) транспьютер Т414 (он же управляющий процессор), 64-разрядный векторный процессор с плавающей запятой, двупортовое ЗУПВ емкостью 1 Мбайт и 16 последовательных каналов связи.

Восемь узловых плат (узловых процессоров), соединенных друг с другом и с системной платой, образуют модуль. Возможности каждого модуля характеризуются производительностью 128*106 Флопс и максимальным объемом ЗУПВ 8 Мбайт, пропускная способность внутри модуля составляет 12 Мбайт/с, а внешние связи системной платы имеют пропускную способность 0,5 Мбайт/с.

Векторный процессор обращается к памяти как к двум банкам векторов, в одном из которых хранится 256 векторов, а в другом – 768, при этом два обращения к памяти производятся за время одного цикла длительностью 125 нс. Сумматор векторного процессора снабжен 6-каскадным конвейером, а конвейер умножителя имеет 5 ступеней при работе с 32-разрядными данными и 7 - при обработке 64-разрядных данных. Модули (т.е. 8 узловых процессоров и системная плата) объединяются друг с другом в виде пространственной решетки и реализуют архитектуру ММПС типа ОКМД.

Рисунок 17.8 - Функциональный узел векторной ММПС

Термин «матричный процессор» используется разными исследователями для описания совершенно разных архитектур. В числе первых это понятие было применено, например, при описании ММПС на основе матричных процессоров МРР (про-

изводилась для NASA фирмой Goodyear Aerospace) и Connection Machine (фирма Thinking Machine Corp.). Эти ЭВМ представляют в своей основе архитектуру ММПС типа SIMD и составлены из большого числа одноразрядных процессоров, а параллельность выполнения команд в них достигается за счет пространственного повторения выполненной команды. Обычный матричный процессор содержит от 16 К процессоров (ММПС МРР) до 64 К процессоров в ММПС Connection Machine. Глубокая пространственная параллельность на матричных процессорах означает практическую независимость скорости исполнения от объема входных данных, т.е. и один, и 500, и 2000 и более входных данных обрабатываются за одно и то же время.

Другим классом суперЭВМ, тесно связанным с матричными процессорами, является подкласс ММПС типа SIMD/MIMD (суперЭВМ PASM, NonVon, DADO). На самом низшем уровне они имеют архитектуру типа SIMD, но, как правило, не состоят из одноразрядных процессоров. Введение параллелизма типа MIMD как надстройки над параллелизмом типа SIMD существенно расширяет возможности суперЭВМ этого класса.

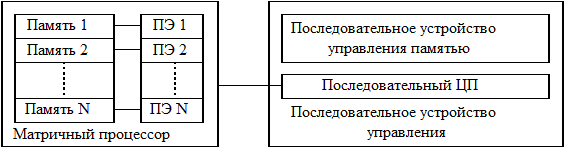

Обобщенный матричный процессор состоит из скалярной последовательной части и направленного массива процессорных элементов (ПЭ) (рис.17.9).

Рисунок 17.9 - Обобщенный матричный процессор

Внутри матричной ММПС должна осуществляться строгая пошаговая синхронизация. Матричный контроллер передает сигналы управления синхронизацией всем процессорам параллельно. Этот уровень синхронизации используется для обеспечения высокой скорости межпроцессорной коммутации и обмена данными. Для организации межпроцессорных обменов широко используются одно- или двумерные сети.

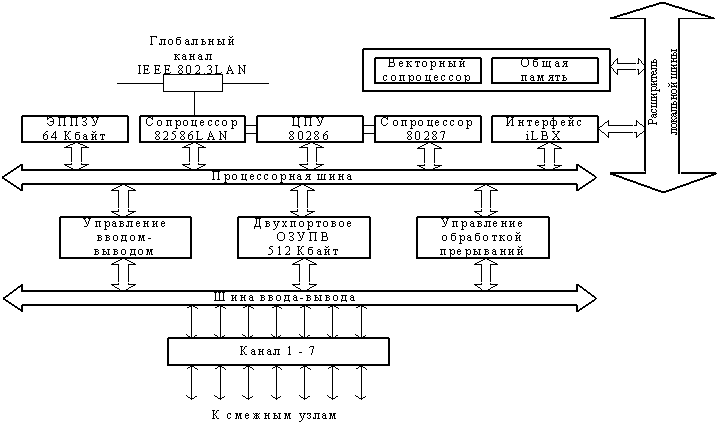

СуперЭВМ с гиперкубической архитектурой INTEL iPSC-VX являлась одной из первых выпущенных систем этого типа. Её максимальная производительность составляет 424*106 Флопс. Надо отметить, что аналогичные и рассмотренные выше суперЭВМ серии Т фирмы FPS и Connection Machine фирмы Thinking Machines появились значительно позже. В системе iPSC-VX используется стандартный МП 80286, сопроцессор 80287, сопроцессор локальной сети (LAN) 82586, семь последовательных каналов ввода-вывода, динамическое ЗУПВ емкостью 512 Кбайт, которые размещены на печатной плате, выполняющие функции узла гиперкуба (рис. 17.10).

Рисунок 17.10 - Структура процессорного узла суперЭВМ Intel iPSC-VX

С помощью расширителя местной шины iLBX-II к узлу может подключаться дополнительная память. Векторный сопроцессор, расположенный на второй плате узла, повышает его производительность до 100 раз при выполнении операций над 64-разрядными скалярными данными. Система iPSC-VX наращивается группами по 16, 32 или 64 узла.

Управляющий процессор куба (микроЭВМ системы 286/310 фирмы Intel) соединяется с каждым узлом посредством локальной сети IEEE 802.3 и обеспечивает реализацию системного интерфейса, а также системы разработки программных средств на основе операционной системы типа XENIX. Наличие семи каналов связи у каждого узла определяет возможность построения гиперкуба с максимальным числом N=27=:128 узлов. Ядро операционной системы размещается в ЗУПВ и обеспечивает реализацию основных сервисных функций.

17.3 Проектирование мультимикропроцессорных систем.

Организация проектирования мультимикропроцессорных систем

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.